Questa Verification IP (QVIP) Course

Do you want to learn how to verify your SoC (System on a Chip) design with Siemens Questa Verification IP (QVIP)? After you complete the new QVIP course, you will be able to generate a complete UVM testbench with QVIP Configurator, and integrate QVIP into existing UVM testbenches. This course is available in self-paced On-Demand Training format (narrated videos, virtual cloud-based labs, knowledge checks, assessment), Live Online Training format (2-day remote class with a live instructor), and Instructor-Led Training format (1-day classroom based).

The best way to create a SoC is with design IP: blocks that connect to standard buses such as AMBA® AXI or PCIe, or memory devices. How do you then check that your chip works correctly with the IP? You need to create stimulus that follows the protocol, but who has time to become an expert at each protocol? The best way to verify your design is with Verification IP that has deep knowledge of the protocol. Siemens QVIP is available for a wide range of protocols such as AXI, AHB, PCIe/NVMe, Ethernet, USB, Serial, plus DRAM and Flash memories.

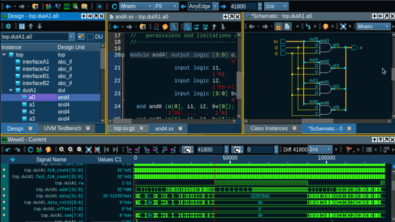

The QVIP course is for engineers who are verifying designs with the above protocols or DRAM and Flash memories. QVIP comes with a library of protocol-specific sequences and test plans. It can drive the bus and check responses with scoreboards and SystemVerilog Assertions. QVIP works with both SystemVerilog and VHDL designs, and easily integrates into a UVM testbench.

Course Content

In the QVIP course, you will learn:

- Overview of Questa Verification IP

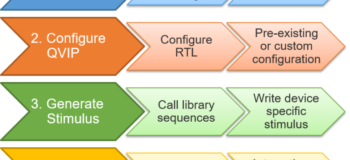

- How to run QVIP Configurator in order to build a UVM testbench

- Configurator inputs including how to connect and configure

- Configurator outputs including the UVM testbench, netlists, and simulation support files

- The structure of QVIP including the interface, bus functional model, assertions, connectivity module and UVM testbench

- How to control QVIP with the configuration classes and structures

- The QVIP scoreboard and its memory

- The slave memory model

- How to learn more about QVIP through the documentation

- Examples included with QVIP

- Basics of AMBA AXI4

Visit the QVIP course page for more information. You can access the on-demand version of this course by subscribing to the Functional Verification On-Demand Training library .

Author: Chris Spear, Principal Instructional Designer, Siemens EDA Learning Services