FPGA Retargeting

FPGA retargeting is an essential element of supply–chain agility in a world without traditional second–sourcing. Since the 1980s, second–sourcing has disappeared to improve supply chain efficiency. Today’s highly–optimized supply chain has worked well. That is until the pandemic disrupted it.

FPGA retargeting is one response to supply–chain difficulties. By creating new versions of a board using different FGPAS, engineers deliver the flexibility to navigate supply–chain issues. The challenge is retargeting the design to a new FPGA without changing its behavior.

FPGA retargeting is more than resynthesizing

Retargeting FPGAs would be easy if designers used only RTL. In that case, we’d retarget resynthesizing in a different vendor’s tool flow. However, FPGA designers usually take advantage of vendor–supplied design IP by dragging and dropping blocks into a schematic and connecting them with custom RTL.

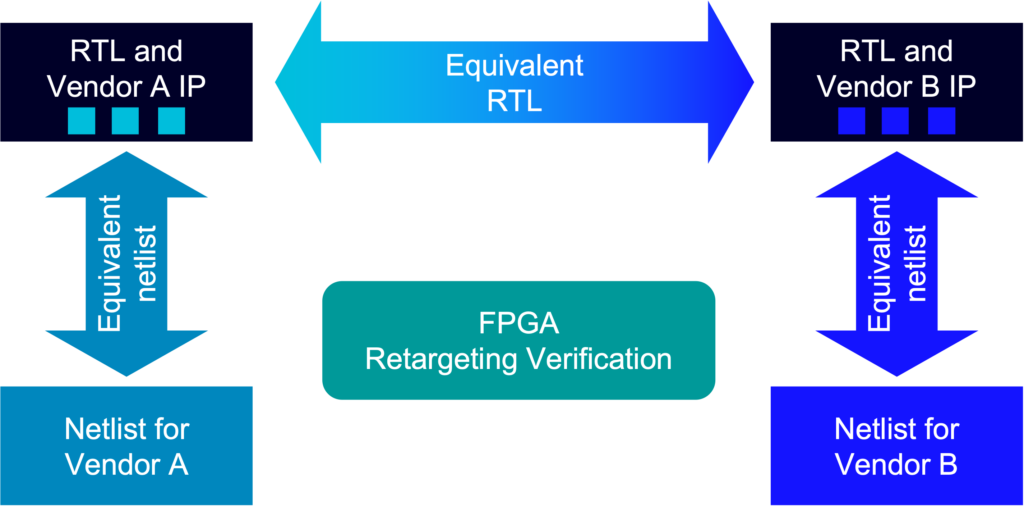

Design IP tied to a specific FPGA vendor or a specific FPGA model means that we cannot simply resynthesize a design. We must create a new version of the design using a new library of IP and then connect our custom RTL to it. How do you verify that the two designs are identical?

FPGA retargeting verification goal

- Ensure that the netlist matches the original RTL.

- Modify the RTL using the new chip’s design IP.

- Ensure that the new RTL matches the new netlist.

One approach to solving this problem is to assume that the RTL and the netlists match and run the RTL against a simulation testbench. This assumes that the testbench has complete coverage and that its stimulus addresses all corner cases. Simulation is a good verification solution, but it doesn’t provide gap–free assurance that both FPGAs match.

FPGA retargeting verification webinar

Another approach to verifying a retargeted design is to prove that the netlists are identical to the RTL and then prove that RTL for each FPGA delivers identical functionality.

The webinar Overcoming Today’s Verification, Supply Chain, and Legacy Technology Challenge Associated with FPGA–based Designs will show you how to deliver gap–free FPGA retargeting verification.

The webinar will outline the verification solutions and retargeting solutions that deliver a solution to deal with FPGA supply chain issues and to extend the life of legacy designs powered by old or obsolete FPGAs. A workflow and methodology will be provided for each scenario, along with real–world case studies.

What You Will Learn:

- The challenges facing FPGA–based designers

- Mitigating FPGA supply chain shortages and legacy design dilemma

- The verification strategies to ensure FPGA–based designs have zero bug escapes

Who Should Attend:

- Design and Verification Engineers and Managers using FPGAs

- Program Managers and Systems Developers