Getting the best of ATPG and LBIST – a Hybrid Test Solution for Autonomous & High-precision IC Test

By Ron Press, Mentor Graphics

Try Hybrid ATPG and LBIST when you need both in-system test and advanced fault detection.

The choice of using logic built-in self-test (LBIST) or automatic test pattern generation (ATPG) has depended on the specific application. If you needed field test, use LBIST. If you needed high-quality production test, ATPG has been the go-to. But what happens when you need them both, say for ICs targeted to safety-critical applications? How much of an area penalty for the extra DFT logic will there be? What if you could get the benefits of using ATPG and LBIST together with less area penalty? That’s the idea behind the Mentor Tessent Hybrid TK/LBIST solution. Let’s review the uses of LBIST and ATPG, then look at the benefits of using them together in an integrated hybrid DFT solution.

One unique value of logic BIST is that the test can be autonomous –initiated and verified in any test environment, even if an external tester is not available. This makes LBIST a necessity for field testing requirements, such as system self-test in a flight control system, satellite, or automobile, as well as some common test environments such as burn-in test. LBIST is also very practical for plug-and-play design support; blocks with LBIST can be reliably reused in any IC without additional run time for pattern generation or risk of unknown coverage.

ATPG, on the other hand, requires the use of an external tester but provides a very high precision of pattern application. By precision, I mean that ATPG can provide very specific values with each pattern, which lets it apply tests on specific paths or control individual clock gaters throughout the design. This means that you can get better defect detection through specialized fault targeting including timing-aware, cell-aware, path delay, bridge, and other types of ATPG. More fault targeting leads to a higher number of patterns, which necessitates the use of embedded compression of the patterns. Today, embedded compression ATPG is the standard production test approach.

The two approaches have recently offered more common features. For example, compressed ATPG now supports a type of plug-and-play capability for blocks that is similar to LBIST reuse with pattern retargeting (using block-level patterns at higher levels). LBIST now supports low-power test similar to what you can do with compressed ATPG.

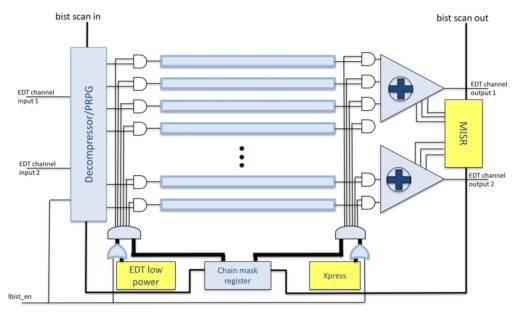

The demand for LBIST has increased in recent years, and in most of these cases, users also want compressed ATPG for the reasons mentioned above. As a result, both compressed ATPG and LBIST are increasingly being used together. Using this ATPG plus LBIST approach has a lot of advantages. If a user has a requirement for field system test, then this approach will always be taken because you get both the better test quality of ATPG and the autonomous testing of LBIST. ATPG quality is better because of x-bounding logic provided for LBIST. However, using both compression ATPG and LBIST has the clear drawback of using more chip area for test logic. The LBIST LFSR (linear feedback shift register) and the compression decompressor (as well as MISR and compression compactor) for ATPG each use different logic, even though their functional purposes are similar. The next step for DFT vendors like Mentor Graphics was to figure out how to combine the logic from embedded compression ATPG and LBIST to enable the hybrid ATPG/LBIST approach without the area penalty. Figure 1 illustrates the combined logic architecture of Tessent Hybrid TK/LBIST.

Figure 1. The logic architecture of the Mentor Graphics Tessent Hybrid TK/LBIST solution. The compression (embedded deterministic test) and LBIST share a majority of the decompressor/LFSR and compactor/MSIR logic.

Aside from reaping area savings through shared logic, you also save area because the hybrid approach requires fewer test points to be added to the design. In traditional LBIST, many test points are sometimes needed to get the required test coverage. However, if ATPG is used with BIST, then you need fewer test points because ATPG can detect the faults that would otherwise require special test points for LBIST to detect.

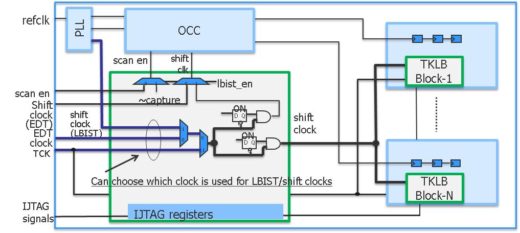

Figure 2. The Tessent Hybrid TK/LBIST solution shares logic within each block and has a top-level LBIST controller to manage clocking and sequences of LBIST tests.

There are many advantages to using compressed ATPG and LBIST together, and having a solution like Tessent that offers combined test logic helps control the area needed by DFT, the test time, and ultimately test cost. The Tessent Hybrid solution described here enables designers to reap the benefits of both ATPG compression and logic BIST, delivering significant efficiency improvements and addressing the requirements for in-system test required for safety-critical applications.

Author

Ron Press is the technical marketing director of the Silicon Test Solutions products at Mentor Graphics Corp.

Liked this article? Then try this –

White Paper: Improve Logic Test with a Hybrid ATPG/BIST Solution