Video: Joe Sawicki on DFT and life-cycle management

At the 2019 International Test conference, Joseph Sawicki, Executive Vice President of IC EDA at Mentor, a Siemens Business, delivered a keynote address about the emerging technical challenges of DFT.

Sawicki starts with the premise that a major factor in testing ICs is the interconnectedness of devices into complex systems. ICs need to operate in the context of smart city sensors, autonomous cars, etc. Investment spending already points to a shift towards AI and machine learning chips and away from traditional chip architectures. As an example, the startup company Cerebras talked about putting together a wafer-scale engine with 1.2 trillion transistors for AI applications.

What does this mean for IC test? In the simple device era, system faults are an inconvenience. A blue screen on your laptop isn’t dangerous, just inconvenient. For these deeply connected systems, though, failures can be critical problems. The number of ICs that require functional safety is increasing, largely driven by automotive demand.

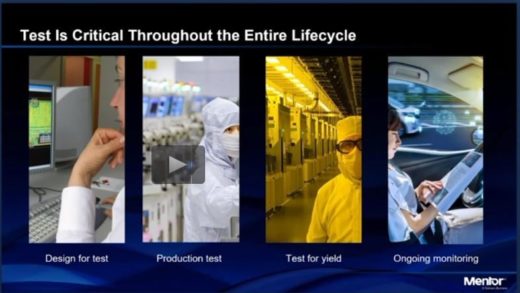

Test becomes more critical throughout the entire lifecycle. To ensure that the devices not only work in the first place but continue to work throughout their operational life, the industry needs to move from thinking about just production test to one that also includes ongoing monitoring.

With more complexity, we’ll need more DFT that keeps up with process nodes, new architectures, growing gate count, and lower pin count. Sawicki discusses the use of high-speed IOs (SERDES) to drive test data to effectively manage test for complex chips. There are also ‘more than test’ issues like quality, security, reliability, and circuit aging. We need to find and manage random errors that can occur in the IC in system. For advanced automotive systems, error detection has to detect the error is a small window of time so corrective action can be taken. A more efficient logic BIST for lifecycle management is called Observation Scan Technology (OST), and it is helping designers of automotive chips reduce in-system test time (DTTI) and area overhead by capturing circuit responses not just during a capture cycle, but also during the shift cycles.

A DFT flow includes design analysis, IP generation and insertion like scan chains and BIST, and generating test patterns. To monitor design aging in-system, companies like STMicroelectronics are looking at inserting test logic that monitors the circuit timing, not just registering logic failures.

DFT has a growing importance in the era of deeply connected electronics. Watch Joseph Sawicki deliver his 2019 ITC Keynote address, From Production Test to Life Cycle Management