An inside look: Innovation, automotive test, and what’s next

Janusz Rajski – Mentor, A Siemens Business

“Our innovations move beyond mere ideas to become convincing products that conquer markets and set benchmarks.”

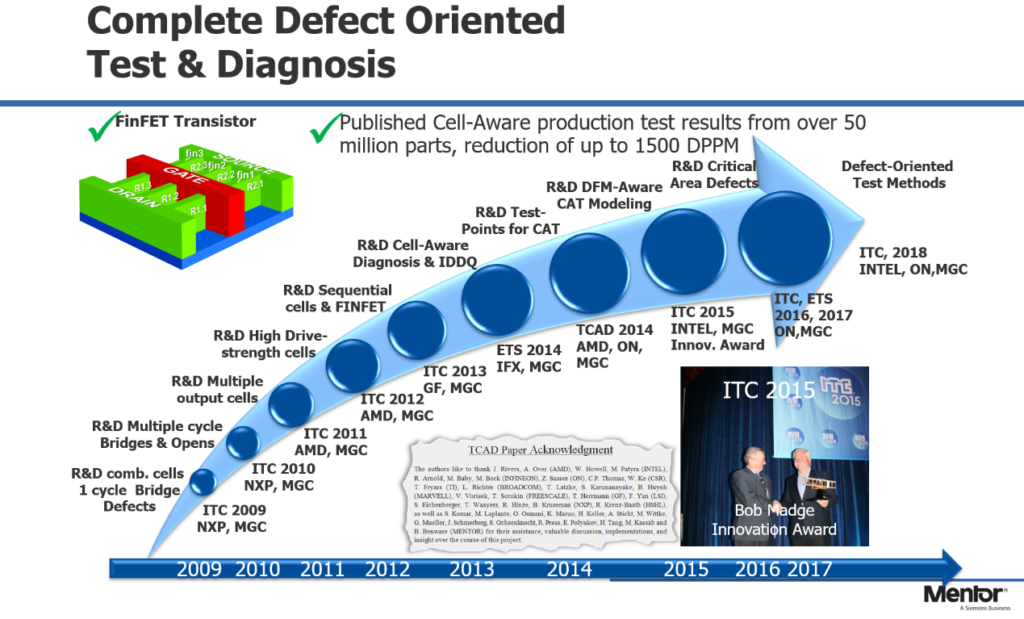

Janusz Rajski, industry luminary and VP of engineering in Mentor’s Tessent test group, presented a keynote at ITC Asia on DFT for automotive reliability. Rajski has years of success in innovating new DFT technologies. He led the development of the industry’s first embedded test compression and of Cell-aware test.

The development of advanced driver assistance systems is fueling the growth of the automotive IC market. One of the biggest challenges in this area is the requirement to ensure functional safety. Where there is an industry need, there will be technological innovation.Rajski focused his keynote on new design-for-test (DFT) solutions that are already being used by leading companies as well as emerging technologies that will be needed to ensure long-term reliability of ICs implemented in new technology nodes. Advanced technology nodes are more complex than what the automotive industry typically used, and introduce new defect types and reliability risks.

The key goals of testing automotive ICs include:

- Ensuring very high-quality manufacturing test.

- In-system test that offer the best trade-offs between the quality of periodic test and its real-time constraints.

Here are some questions and answers stemming from Rajski’s keynote.

Q: What are the unique DFT challenges and requirements for the Automotive IC era?

Janusz: There are two unique requirements for automobile chips. First, the ICs are expected to have high reliability, zero defects, not just during the manufacturing test at the time-zero of the ICs, but also the 10 to 20 year duration of the automobile life. During the normal car operation, it is very important to perform periodic test and ensure the ICs are still functional correctly, and signal any abnormal conditions. Second, automobile ICs are sensitive to area overhead for DFT and test time in addition to high test quality.

Q: What DFT tools does Mentor offer to address the challenges and opportunities of the Automotive IC market?

Janusz:For high-quality test, Mentor has been working on detecting the defects beyond the tradition fault models, like the stuck-at and transition faults, for over 10 years. This research and development led to our Cell-aware test capability, which reduces the defect escape for high-reliability chips. With the cumulated testing on over 50M dies with various customers, the effectiveness of cell-aware test has been well validated. We continue to further enhance the cell-aware model as well. This year, we are going to release an automobile-grade ATPG to bring the test quality of the automobile ICs to the next level.

For manufacture test, TestKompress (TK) is today’s industry standard solution. The hybrid TK/LBIST methodology is effectively addressing the needs for in-system test. The on-chip DFT logic is shared between the EDT and LBIST, which minimizes the additional area that would be needed for LBIST. In addition, we introduced VersaPoint test points, which are designed specifically to reduce the pattern count and test time for both the manufacture test as well as the in-system test in hybrid TK/LBIST methodologies.

Due to the artificial intelligent (AI) trend of new automobile systems, those complex ICs may contain hundreds, or even thousands, of cores. The Tessent hierarchical test methodology is designed to handle such large designs. Tessent can create patterns at the core-level very efficiently, then re-target and merge patterns at the top-level to derive the final patterns. The Tessent hierarchical test approach can handle complex AI chips with 10X speedup compared to the traditional whole-chip approach while creating more compact patterns.

The solutions I mentioned above are mainly for the digital part of the ICs. For memory, it is as important to test them periodically while driving. Our non-destructive MBIST solution is designed for such scenario. It tests the memory piece by piece by stealing couple cycles here and there without impacting the normal circuit operation.

And don’t forget about the analog part of the circuit. Mentor has released a new product called Tessent DefectSim which fault simulates the analog circuit and reports the analog design test coverage. In addition, it pinpoints the redundant test sequences, those that don’t improve the test coverage and can be eliminated to save test time. It now also reports the functional quality metrics for ISO 26262 requirement.

Q:Talk about your definition of “innovation.”

Janusz:The secret is always the team. We assemble a team with the best people in this industry for ATPG, compression, memory and logic BIST, analog test, diagnoses, and yield learning aspects. Not only do our products reflect this, but also our publications. The Mentor Tessent team always shows up at the top conferences like ITC or other test and diagnosis symposiums.

Second, the culture of innovation is always within the team. In a very deep way, we have a track record of doing innovative research and then translating that into products. This innovation culture is shared between our team members. The culture of innovation gives us the capability to face new challenges. In addition, we have to focus on our customer’s real problems. Even if a problem has no known solution, we have the confidence to solve it and create the value for our customers because of the team.

Twenty years ago, the semiconductor industry said that the cost of testing was going to absolutely kill them. The chief technology officer from Intel predicted that in 15 years, the cost of manufacturing per transistor would be lower and the cost savings would transfer to cover the cost of testing, and finally the two would be almost the same. Our team was the first to see it, because of the capability and our focus. As a result, we introduced TestKompress, the first commercial embedded compression and solved the test cost issue for the IC industry.

One more example, when transitioning to a new technology node the quality of the IC manufacturing is not always so good and it takes a long time to debug the yield issues manually. We focus on solving this problem by developing the diagnoses and yield assist tools. When you find a problem and focus, with a confidence team, you can create value for your customers.

We do our own research, and in many cases we do industry-leading research. The next step is collaboration with semi-conductor companies to validate our solutions. Since Mentor doesn’t own the silicon, we cooperated with many companies with over 50 million dies for the Cell-Aware test to ensure the quality improvement of the solution.

TestKompress was one of the three products that has been granted a Stephen Swerling Innovation Award during Mentor’s whole history, and it helped Mentor Graphics achieve the No.1 position in design-for-test. Innovation will not only affect patterns, but also business and marketing share.

Q: There has been very fast growth in semiconductors during the last 20 years. What advice can you give young engineers around the world about the industry?

Janusz:In the last 20 years, we made great progress in DFT. On the other hand, take aviation industry as example, we are still at subsonic speed, but soon will reach the barrier and go supersonic, because the new application as AI and more complex technology. In addition to traditional test, we are doing system test, reliability during the device’s life cycle, function safety, and in-field repair. All these types of testing need to be combined. There’s lots of challenges and opportunities for the research community, as well as career opportunities for people who are getting into this area.