Smarter DFT tackles design scaling

By Ron Press and Vidya Neerkundar – Mentor, A Siemens Business

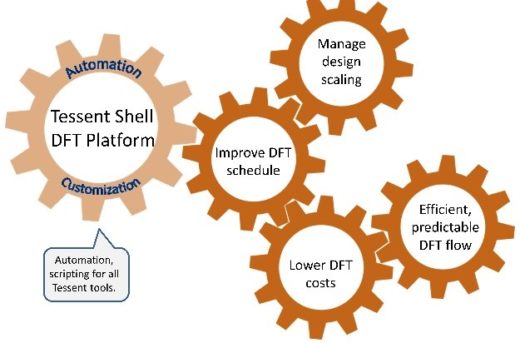

Is your DFT work keeping up with design scaling? Larger designs and tight schedules demand a smarter approach to DFT automation and the adoption of plug-and-play DFT methodologies.

The reality of DFT for large and complex SoCs has introduced new risk into design schedules. DFT teams end up in the critical path to tape out while waiting for portions of the design to be complete, and there are more DFT integration steps than ever before. That’s why adopting a DFT methodology with a well-defined infrastructure and automation is essential for any chance of success. Automation is paramount to making these steps very reliable and removing an insurmountable number of iterations to fix DFT integration steps that might kill the schedule.

The reality of DFT for large and complex SoCs has introduced new risk into design schedules. DFT teams end up in the critical path to tape out while waiting for portions of the design to be complete, and there are more DFT integration steps than ever before. That’s why adopting a DFT methodology with a well-defined infrastructure and automation is essential for any chance of success. Automation is paramount to making these steps very reliable and removing an insurmountable number of iterations to fix DFT integration steps that might kill the schedule.

The traditional approaches to DFT work on huge designs pose problems of repeatability and reliability. With more DFT steps, the overall rate of success declines unless the rate of success at each step is extremely high. So, how do you ensure an extremely high rate of success at each step in the DFT flow?

The best path to success in DFT is to use a well-design DFT methodology. For large designs, this means adopting a hierarchical DFT, which removes the effort of pattern generation on the full design and enables concurrent test insertion on multiple blocks. Test patterns generated with Tessent TestKompress for a block do not need to be regenerated during chip-level pattern generation; they can be directly reused or “retargeted.” This ability to retarget block-level patterns through multiple levels of hierarchy is itself a good enough reason for many designs to use hierarchical flows. After all, when the patterns do not need to be regenerated, you save not just time and resources, but you also improve reliability, which in turn increases success.

In addition to a strong DFT methodology, furthering automating as many DFT steps as possible also reduces risk and improves the efficiency and reliability of the entire design flow. The Tessent product family of tools all operate on the same tool environment, called Tessent Shell, and share the same database. This allows for easier customization and more built-in automation, including:

- Memory and logic BIST scannability: Tessent BIST products automatically tell other Tessent products how to configure the BIST logic for use during scan configuration and test

- Boundary scan logic reuse: boundary scan logic is automatically configured to be efficiently utilized during scan test

- DRCs for pattern retargeting: much of the knowledge developed to support hierarchical DFT pattern reuse/retargeting is contained in how block-level data is shared with the top level for reuse. This includes many DRCs to ensure the block-level patterns can be appropriately applied

- Pattern retargeting automation: block-level pattern retargeting automatically adjusts when it recognizes inversions, pipelines, and more in the top-level embedding

- IJTAG setup porting: since the Tessent infrastructure can be implemented with IJTAG, block-level pattern setup is automatically embedded in the top-level setup

Designs continue to scale and add new challenges to design and test teams. Smarter DFT methodologies and powerful, flexible automation boost the overall DFT success rate by reducing risk and ensuring reliability and predictability in DFT flows. Hierarchical DFT enables concurrent DFT development and integration, similar to how other design development work is done. A plug-and-play infrastructure that enables hierarchical DFT, extensive automation with easy customization dramatically improves the reliability and predictability of DFT.

To learn more about improving DFT flows for large and complex designs with a smarter DFT infrastructure, download this new whitepaper Smart DFT infrastructure and automation are key to managing design scaling