What Lies Ahead for System-Technology Co-Optimization (STCO) in 2026

The race to build ever more powerful and energy-efficient AI chips has been underway for years, but 2026 is shaping up to be a true inflection point. The rapid rise of 3D heterogeneous integration is fundamentally changing how AI systems are architected, optimized and manufactured.

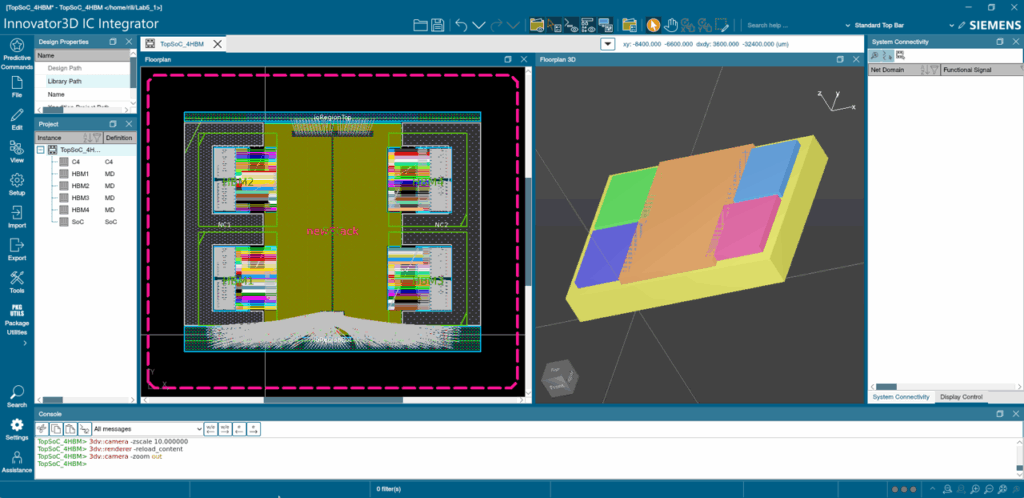

As these 3D designs scale from tens of millions of connections to hundreds of millions — and soon, billions — traditional design flows make it difficult for IC and package teams to capture reliability issues early and optimize system performance holistically.

This is why System-Technology Co-Optimization (STCO) is no longer optional for next-generation AI systems. STCO shifts optimization from isolated domains to the system level, enabling architecture, packaging, power delivery, and thermal-mechanical strategies to be co-designed from the outset. Read on as we examine the latest advances in STCO and the key 3D IC design trends shaping 2026.

How is STCO different from DTCO?

For years, the semiconductor industry relied on Design-Technology Co-Optimization (DTCO) to push scaling forward. DTCO breaks down the traditional boundary between circuit design and manufacturing process technology. It enables closer collaboration among IC designers, EDA vendors, foundries, and equipment suppliers to co-optimize designs for a given process node.

System-Technology Co-Optimization (STCO) extends this methodology beyond the device and circuit level to the system level. In addition to circuit-process interactions, STCO incorporates 2.5D/3D IC packaging, die-to-die interconnects, system architecture, and even software considerations to determine how a complex system should be partitioned, implemented, and reassembled to achieve optimal performance, power, area, cost, and reliability.

Trend 1: 1000-chiplet integration makes STCO a necessity

As designs scale from “a few chiplets plus HBM” toward wafer-level, modular systems, the industry is rapidly approaching a future where integrating hundreds—or even 1,000—chiplets in a single package is no longer science fiction. Today, advanced packages already exceed 50 million pins, and that number continues to grow. Looking ahead, designs with hundreds of millions of pins are well within reach. At this scale, no one “sees” the whole design anymore. Spreadsheets and point tools quickly become inadequate. You’re dealing with: tens or hundreds of dies, multiple process nodes and memory stacks and millions of power/ground pins and ultra-dense die-to-die interfaces.

That’s why true System-Technology Co-Optimization (STCO) becomes non-negotiable. By breaking the system into smaller manageable abstractions across hierarchy, teams can work more effectively with massive design data. In addition, STCO enables designers to analyze predictive models and explore system behaviors across multiple domains, such as signal integrity and power integrity, testability, thermal and mechanical integrity (stress, warp, coplanarity).

In traditional flows, critical issues often surface after physical design is largely complete, at which point correcting such issues requires massive changes, making a complete redesign faster. But redesigning a complex package from scratch is also expensive and can be economically non-viable, with the impacts on schedule, cost, and competitive positioning. STCO enables a true left shift, exposing architectural risks when they can still be addressed with manageable cost and schedule impact.

Trend 2: AI becomes embedded in STCO workflows

As 3D IC systems grow in scale and complexity, AI will be increasingly embedded into STCO workflows. AI can help designers evaluate thousands of architectural choices, including interconnect types, areas, electrical, thermal and mechanical tradeoffs. This capability is already being applied at Siemens today in AI-driven, multi-domain optimization tools within the STCO flows.

AI will also help mitigate the semiconductor industry’s growing talent shortage. No modern 3D IC succeeds without carefully balancing signal integrity, power integrity, thermal, and mechanical effects, yet the supply of deep domain experts is increasingly constrained. Industry estimates suggest the semiconductor sector will require more than one million additional skilled workers by 2030. AI helps scale scarce expert knowledge, making advanced, multi-domain analysis accessible earlier in the design flow and to a broader set of engineers. Signoff-quality verification, root-cause analysis, and methodology development will continue to rely on experienced specialists. The fundamental change AI brings is productivity: faster exploration, faster simulation, and earlier insights into the design process.

Trend 3: Flows, standards, and teams converge

Traditional DTCO approaches and piecemeal STCO approaches (link and component level) typically do not model the entire system and are, therefore, not suitable for system-level planning. Design engineers are left blind to the impact of decisions at the lower levels on application performance and power.

To scale STCO, progress must occur across tools, standards, and organizations – and significant convergence is actively taking place:

- On the tooling side: The EDA industry is moving toward system-level “cockpit” platforms that orchestrate early planning, system and package floorplanning, chiplet interface definition, pre-layout analysis, and handoff to layout, multiphysics analysis, and test. Rather than forcing a “one tool does everything” model, momentum comes from tighter integration across electrical, thermal, mechanical, and test domains, enabling coordinated analysis while preserving domain depth.

- On the standard side: Alignment is already emerging. Initiatives such as TSMC’s 3Dblox provide a common abstraction for representing 3D IC assemblies. While not yet a formal IEEE standard, 3Dblox has gained broad industry acceptance and support across major EDA vendors, serving as a practical foundation for interoperability and cross-tool integration.

- On the organizational side: STCO is reshaping how teams work. Leading companies developing advanced 3D ICs are forming cross-domain teams that bring together chip architects, silicon designers, package engineers, SI/PI and thermal experts, and test engineers around a shared system model. Organizations that maintain rigid silos between silicon and package teams increasingly feel the consequences, as late-stage cross-domain issues trigger schedule slips and costly re-spins. In sectors such as automotive, where safety, reliability, and lifecycle requirements are stringent, the pressure to break down silos is even greater.

Conclusion

As we look towards 2026 and beyond, it’s clear that STCO is the fundamental shift required to unlock the full potential of next-generation AI. By enabling a holistic, system-level approach from architecture to manufacturing, STCO empowers designers to navigate the immense complexity of 3D ICs with unprecedented efficiency. This methodology ensures that critical issues are addressed early, optimization for power, performance, area, and cost, while guaranteeing reliability in an era of multi-hundred-chiplet designs.

To dive deeper into the concepts and tools behind this shift, read my latest white paper on STCO.

Per Viklund

PerViklund is Systems Architech Director at Siemens EDA, responsible for IC packaging and RF/microwave product strategy and technology. He has more than 40 years of experience with electronic design and EDA and has spent the past 39 years focusing on high-density advanced packaging (HDAP) and RF/microwave design solutions.