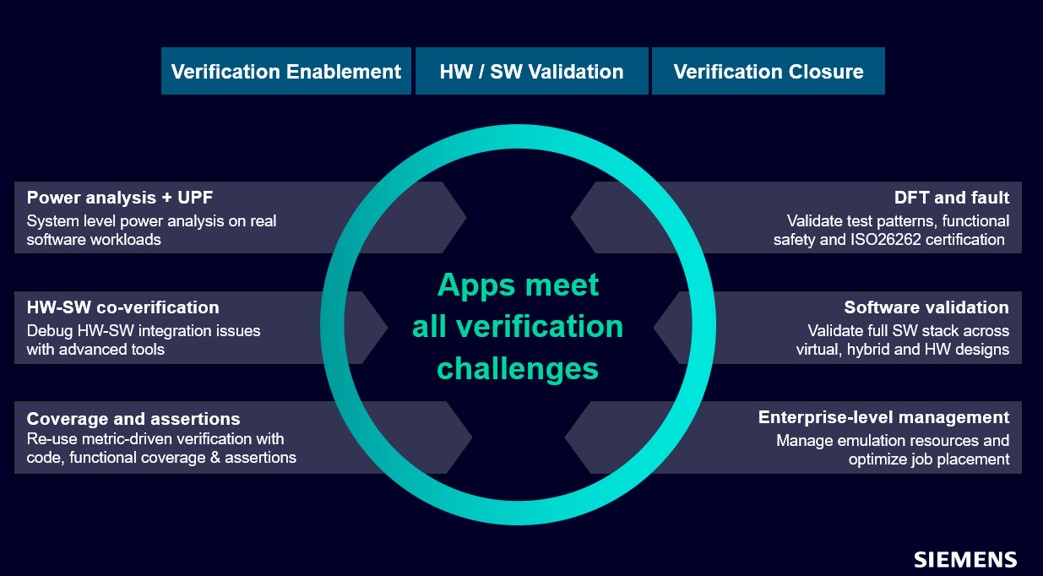

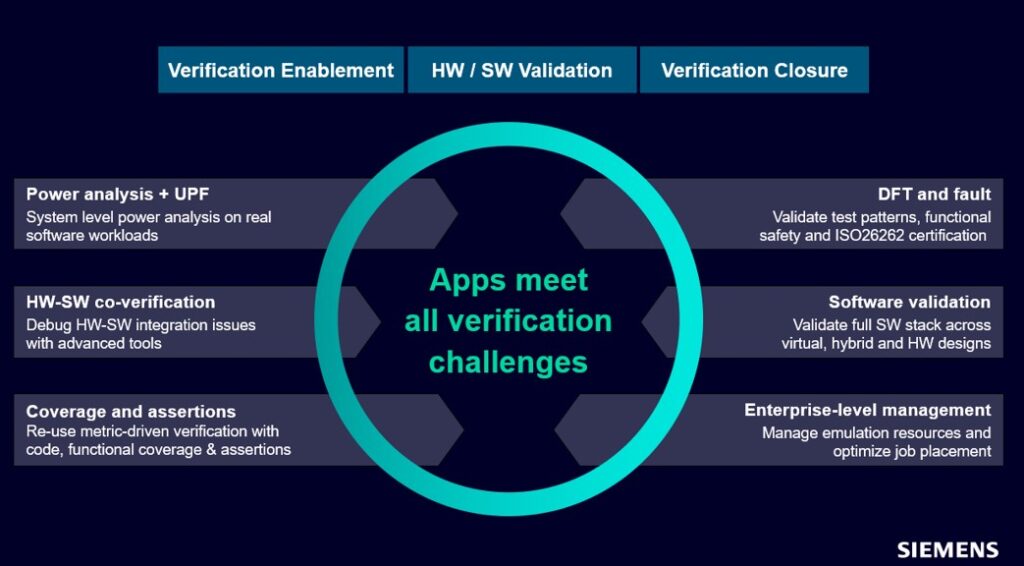

The Veloce Ecosystem: Applications Targeted to Solving End User Challenges

In the rapidly evolving semiconductor and electronic design world, hardware-assisted verification (HAV) has become an indispensable part of the design process. The use of hardware platforms like emulators and FPGA-based prototyping systems to enhance the verification and validation process, ensure designs meet their specifications efficiently and effectively. But what about the end users’ challenges and use cases? What tools and technologies are available to help enable a more efficient verification/validation environment or help with verification closure? What about teams who are tasked with HW/SW Co-verification tasks? Do they have the necessary tools and applications to get their job done? I think asking these critical questions and examining the use cases is important to providing a comprehensive solution that addresses the verification and validation team’s needs. To help understand how Siemens EDA is solving this challenge, let us delve into some key use cases of HAV, enabled by Veloce Apps.

Software development, debug, and validation

It is well known that Hardware-assisted verification plays a crucial role in software development, particularly in the initial stages of chip design. By using emulators, developers often run full workloads/software on hardware models, allowing them to identify and fix issues before the physical hardware is available. By providing full reference designs that operate stand-alone, or in a hybrid execution model with HAV platforms, one significantly accelerates the development cycle and reduces the risk of costly post-silicon bugs because system-level workloads were not run.

Debugging

Debugging complex hardware designs and system-level interactions can be daunting. HAV tools provide a robust environment for identifying and resolving such issues. Emulators offer visibility into the hardware’s internal states, enabling engineers to trace and diagnose problems more effectively than traditional simulation methods. This capability is especially valuable for catching elusive bugs that might only appear under specific conditions.

Analysis

Understanding how a design performs under various workloads is critical for optimizing performance and power consumption. HAV tools allow designers to simulate real-world workloads and analyze the system’s behavior in detail. This analysis helps fine-tune the design to meet performance targets and ensures the system can handle the expected operational demands.

Verification Closure

Achieving verification closure—ensuring that a design meets all its specifications and is free of critical bugs—is a significant milestone in the design process. HAV tools accelerate this process by providing high-speed, high-capacity verification environments. They enable comprehensive testing, including corner-case scenarios that might be impractical to test with traditional methods. This thorough testing is essential for ensuring the reliability and robustness of the final product.

Acceleration

The nature of HAV platforms is to accelerate the execution of tasks of the verification and validation team. But is simply running on the emulation or prototyping platform enough? It is just a start. I would argue additional methodologies targeted at reducing not only the wall clock time for execution, but also automating test bench debug are critical for increasing the efficiency of the verification and validation environment. Additional techniques around checkpointing and restoring elements of the verification environment further improve the efficiency of the verification and validation team. These are just some ways the Veloce Ecosystem decreases the wall clock time required to get your job done.

Hardware-assisted verification is a powerful technology that addresses many challenges in modern chip design. From accelerating software development and enhancing debugging capabilities to enabling detailed workload analysis and ensuring verification closure, Veloce Apps are indispensable for today’s engineers. As design complexities continue to grow, the role of HAV in ensuring successful, timely, and cost-effective product development will only become more critical. In the coming series of blogs, my colleagues and I will discuss in detail several of the Veloce Apps in the Veloce Ecosystem and share how they help address our customer challenges.

Andy Meier is a Principal Product Manager within the Hardware Assisted Verification Division at Siemens EDA. He has 20+ years of experience in the semiconductor industry, specifically in the design and verification space. He has worked as a verification lead at both start-up and large enterprise organizations. He holds a Bachelor of Science in Engineering and Computer Engineering from Worcester Polytechnic Institute in Worcester, Mass.