Article Roundup: Learning to Live with the Gaps Between Design and Verification, PSS, Test Realization and Reuse, Mentor Offers Pads Professional Design Software Free to Students, Instructors, Automate P2P resistance checking for better, faster ESD protection, Siemens and Valor: Two Complementary DFM Technologies

- Learning to Live with the Gaps Between Design and Verification

- PSS, Test Realization and Reuse

- Mentor Offers Pads Professional Design Software Free to Students, Instructors

- Automate P2P resistance checking for better, faster ESD protection

- Siemens and Valor: Two Complementary DFM Technologies

Learning to Live with the Gaps Between Design and Verification

SemiWiki

This article highlights the presentation given by Mentor at DVCON that acknowledges the gaps in the design flow and in some cases embraces the designers to improve the speed and effectiveness of the verification process. The author talks about the video which examines several gaps in development processes that can result in verification escapes, and suggests solutions that can prevent bugs from finding their way into customer deployments.

This article highlights the presentation given by Mentor at DVCON that acknowledges the gaps in the design flow and in some cases embraces the designers to improve the speed and effectiveness of the verification process. The author talks about the video which examines several gaps in development processes that can result in verification escapes, and suggests solutions that can prevent bugs from finding their way into customer deployments.

PSS, Test Realization and Reuse

SemiWiki

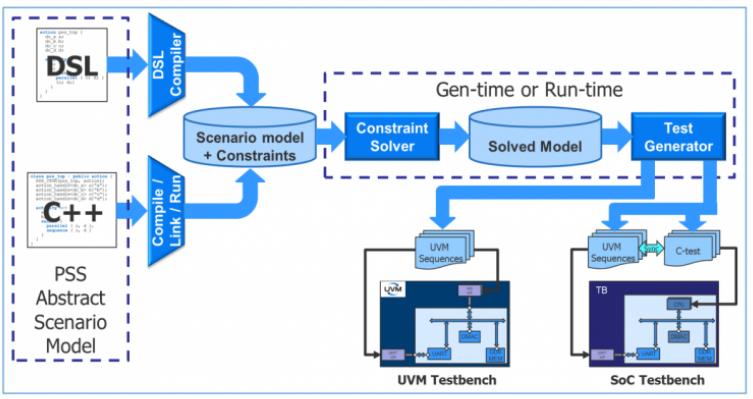

The article compares and contrasts the template and procedural interface (PI) approaches and comes down on the side of the PI for flexibility, ease of management and better up-front error-checking. The PSS language features used to model test intent are heavily constraint-based, and capture value relationships that model a test space. The author explains that the Accellera PSS language enables test intent to easily be combined, making test intent portable across a range of execution platforms and reusable across a range of levels of verification

The article compares and contrasts the template and procedural interface (PI) approaches and comes down on the side of the PI for flexibility, ease of management and better up-front error-checking. The PSS language features used to model test intent are heavily constraint-based, and capture value relationships that model a test space. The author explains that the Accellera PSS language enables test intent to easily be combined, making test intent portable across a range of execution platforms and reusable across a range of levels of verification

Mentor Offers Pads Professional Design Software Free to Students, Instructors

PCD&F.com

Mentor is offering students and instructors a free student edition of its premium PADS Professional Design Suite (v. 2.7) desktop software for electronics design and analysis. PADS Professional combines capture, layout, signal integrity analysis, and 3-D. This article highlights the key role played by the software for engineering students and more.

Mentor is offering students and instructors a free student edition of its premium PADS Professional Design Suite (v. 2.7) desktop software for electronics design and analysis. PADS Professional combines capture, layout, signal integrity analysis, and 3-D. This article highlights the key role played by the software for engineering students and more.

Automate P2P resistance checking for better, faster ESD protection

TechDesignForum

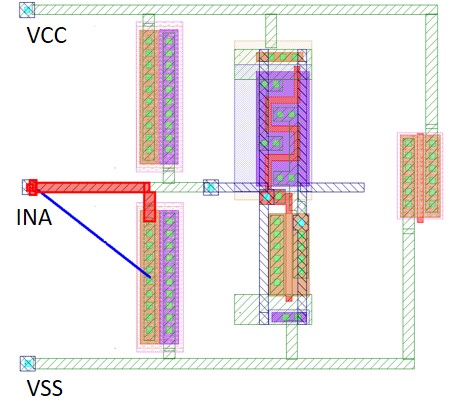

With advanced semiconductor process nodes, and the smaller transistor and interconnect feature sizes prevalent in leading-edge IC designs, finding and eliminating ESD problems quickly and efficiently is critical to ensuring the reliability of ICs while maintaining production schedules. Checking the resistances of ESD discharge paths in a layout to determine if they are within pre-defined design thresholds plays an essential role in ESD protection in IC chip designs. In this article, the author highlights the need to check ESD path resistance, debug resistance bottlenecks and more.

With advanced semiconductor process nodes, and the smaller transistor and interconnect feature sizes prevalent in leading-edge IC designs, finding and eliminating ESD problems quickly and efficiently is critical to ensuring the reliability of ICs while maintaining production schedules. Checking the resistances of ESD discharge paths in a layout to determine if they are within pre-defined design thresholds plays an essential role in ESD protection in IC chip designs. In this article, the author highlights the need to check ESD path resistance, debug resistance bottlenecks and more.

Siemens and Valor: Two Complementary DFM Technologies

iConnect007

In this article, Andy Shaughnessy, Director of portfolio development explains that the integration of Valor solutions with Siemens gives the designers, a full portfolio to do electronic design all the way through manufacturing. He also adds that Valor tools is integrated into Opcenter Execution, which provides a complete solution all the way through to box build.