Article Roundup: How MaxLinear got faster signoff DRC while optimizing reliability and manufacturability, HLS Powers AI Revolution, Earlier is Better in Latch-Up Detection, Embedding Software Algorithms in New Chip Applications Calls for New Verification, Improving Circuit Reliability

- How MaxLinear got faster signoff DRC while optimizing reliability and manufacturability

- HLS Powers AI Revolution

- Earlier Is Better In Latch-Up Detection

- Embedding Software Algorithms in New Chip Applications Calls for New Verification Solutions

- Improving Circuit Reliability

How MaxLinear got faster signoff DRC while optimizing reliability and manufacturability

TechDesignForum

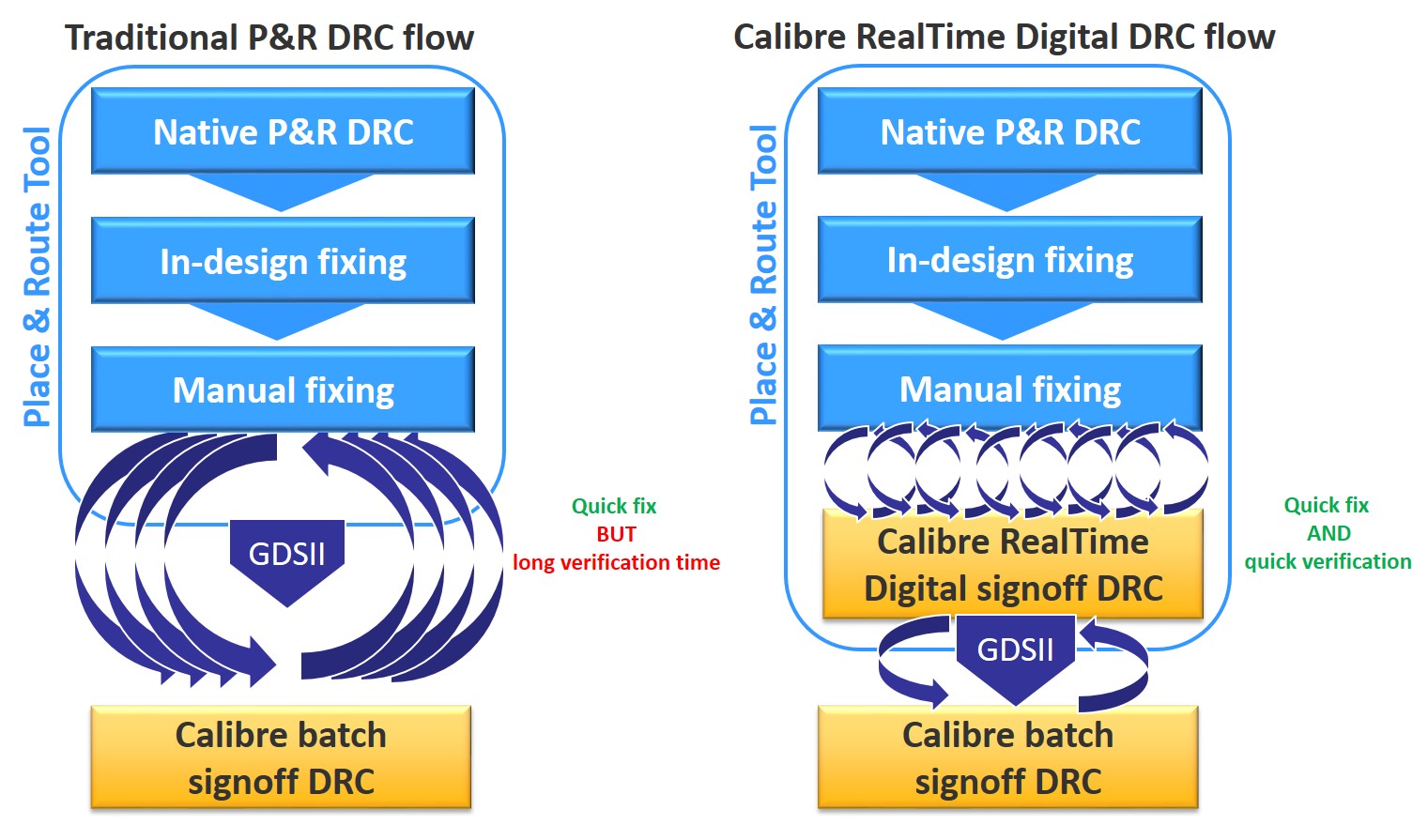

The Calibre RealTime Digital interface enables P&R engineers at MaxLinear to perform targeted, on-demand Calibre signoff DRC during the digital design flows. This article throws light on the various design challenges & opportunities MaxLinear’s chips offers along with via selection and addressing multi-patterning errors. By enabling fast, iterative signoff DRC checking and fixing during floor planning and placement, the Calibre RealTime Digital interface not only reduces batch DRC iterations, but also eliminates late-stage issues during final physical verification signoff that are exponentially harder to fix.

HLS Powers AI Revolution

EEJournal

This article focuses on HLS powering AI revolution and its promises in the future of AI. The author talks about how the combination of HLS and FPGA promised to form a kind of new compiler and processor pair that could take C/C++ code and create an engine that could trounce conventional processors in performance and power efficiency. He also draws importance on how a typical simple but computationally-demanding algorithm put through the HLS-to-FPGA flow could easily beat a conventional software-on-CPU implementation of the same algorithm by orders of magnitude.

Earlier Is Better In Latch-Up Detection

SemiEngineering

Traditional latch-up detection occurs late in the design flow, requiring costly and time-consuming late-stage physical layout changes. By running automated topology-based latch-up verification on the schematic netlist during early design phases, designers can quickly identify sensitive latch-up scenarios. Most of these latch-up conditions can be quickly resolved through circuit design changes without any major impact on IC implementation, preventing expensive delays and emergency rerouting. This article explains the methodologies and need of traditional latch-up protection, spacing protection, guard ring protection, topology-driven latch-up protection and more

Embedding Software Algorithms in New Chip Applications Calls for New Verification Solutions

EEWeb

When it comes to data movement, traditional memory architectures serving the venerable CPU as well as their limited bandwidth kill performance and propel power consumption. The solution is to migrate software algorithms from CPU-based execution to a hardware-accelerated implementation optimized for power, performance, and area. This article talks about why verification overhaul is necessary to address new market opportunities, and the importance of having a system-level flow for SoC architecture analysis.

Improving Circuit Reliability

SemiEngineering

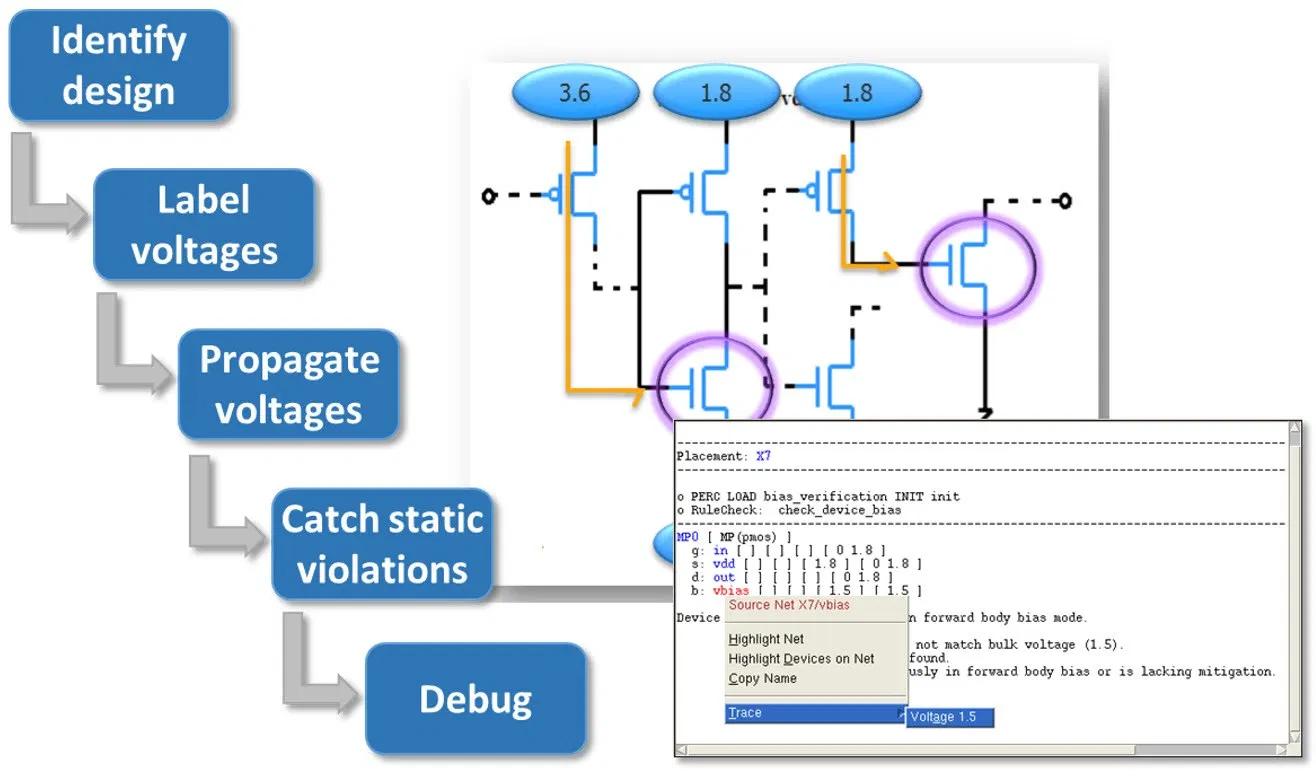

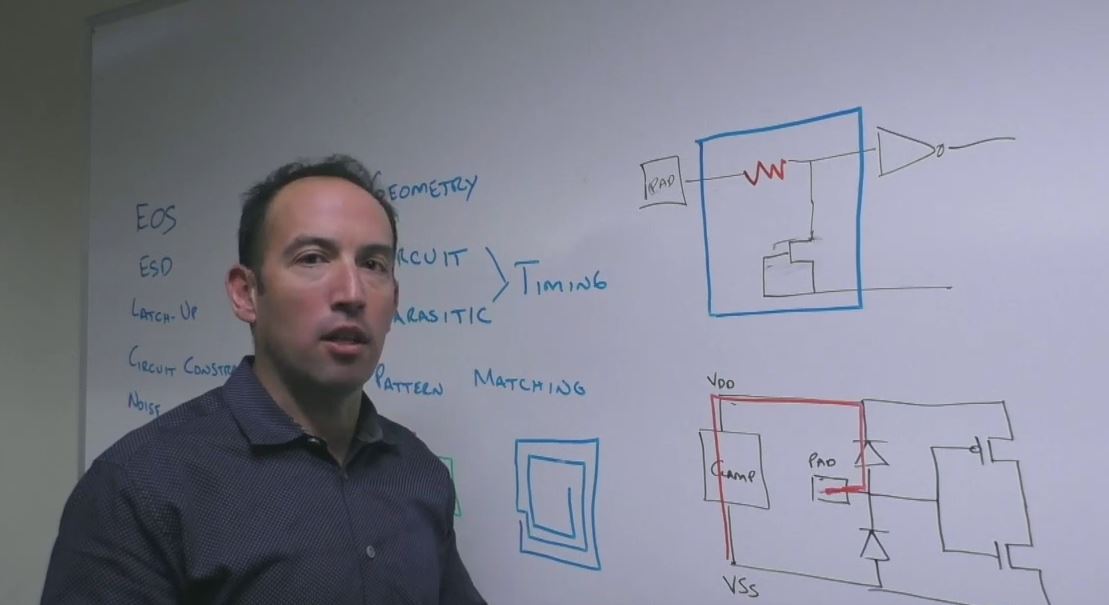

Carey Robertson, product marketing director at Mentor, a Siemens Business, examines reliability at advanced and mainstream nodes, particularly in automotive and industrial applications, what’s driving growing concern about the reliability and fidelity of analog circuits, and the impact of running circuits for longer periods of time under different voltage and environmental conditions.