Article Roundup: Joe Sawicki on DFT and life-cycle management, Aging Analysis Standard Solidifies Through Collaborative Effort, Mentor Masterclass on ML SoC Design, Staying True to the Mission to Fight COVID-19, Hardware Emulation Future is Exciting

- Joe Sawicki on DFT and life-cycle management

- Aging Analysis Standard Solidifies Through Collaborative Effort

- Mentor Masterclass on ML SoC Design

- Staying True to the Mission to Fight COVID-19

- Hardware Emulation Future Is Exciting

Joe Sawicki on DFT and life-cycle management

MentorBlogs

This blog throws light on the emerging technical challenges of DFT. Joseph Sawicki, Executive Vice President of IC EDA at Mentor, a Siemens Business emphasizes that ICs need to operate in the context of smart city sensors, autonomous cars, etc. with investment spending already points to a shift towards AI and machine learning chips and away from traditional chip architectures. The number of ICs that require functional safety is increasing, largely driven by automotive demand. He further stresses on how DFT has a growing importance in the era of deeply connected electronics and how Test is critical throughout the entire lifecycle.

Aging Analysis Standard Solidifies Through Collaborative Effort

SemiEngineering

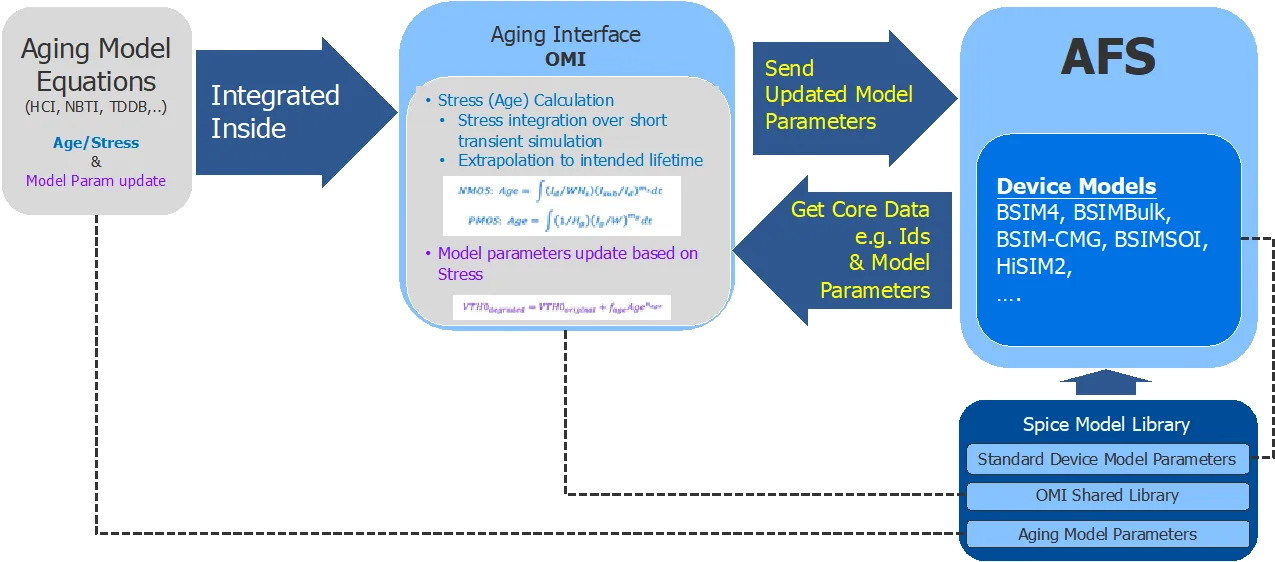

With close collaboration with Mentor, Samsung Foundry developed an aging model with the native OMI, based on the reliability equations from the 7nm advanced technology node. The model was then verified with Analog FastSPICE (AFS), Mentor’s nm-accurate SPICE simulator, and other simulators in terms of accuracy and performance. Through a collaborative effort, Mentor and Samsung are working together to ensure Qualcomm and other customers develop a successful product development roadmap with strong support for design automation, quality, and product reliability across all process technology nodes from planar technology to FinFET technology and beyond.

Mentor Masterclass on ML SoC Design

SemiWiki

Convolutional Neural Networks (CNN) have been the ML networks most often used for object detection and classification. Catapult HLS provides a number of high-level optimizations such as automatic memory partitioning for creating complex on-chip memory architectures needed by the ML engine to achieve performance goals. While ML algorithms and hardware has definitely moved into the mainstream, designers have only skimmed the surface of what is possible. The complexity of the next-generation hardware and algorithms needed for tomorrow has already exceeded what can be done today. This article talks about how the Tensorflow system is made to run inside a Docker container with an appropriate version of the Ubuntu OS and Tensorflow framework, which simplifies installation of the AI framework.

Staying True to the Mission to Fight COVID-19

MachineDesign

This article encourages students who are encountering distance learning, perhaps for the first time, to make use of the 12-month license of Mentor’s PADS Professional PCB design software apart from Siemens Digital Industries Software’s free Solid Edge virtual design software to bring their ideas to life.

In these hard times, we’re reminded that our technology is only as powerful as our people deploying and maintaining it. Siemens USA CEO, Barbara Humpton says that amid all the troubling news that surrounds us, the stories of human ingenuity, compassion and service are truly powerful.

Hardware Emulation Future Is Exciting

EEWeb

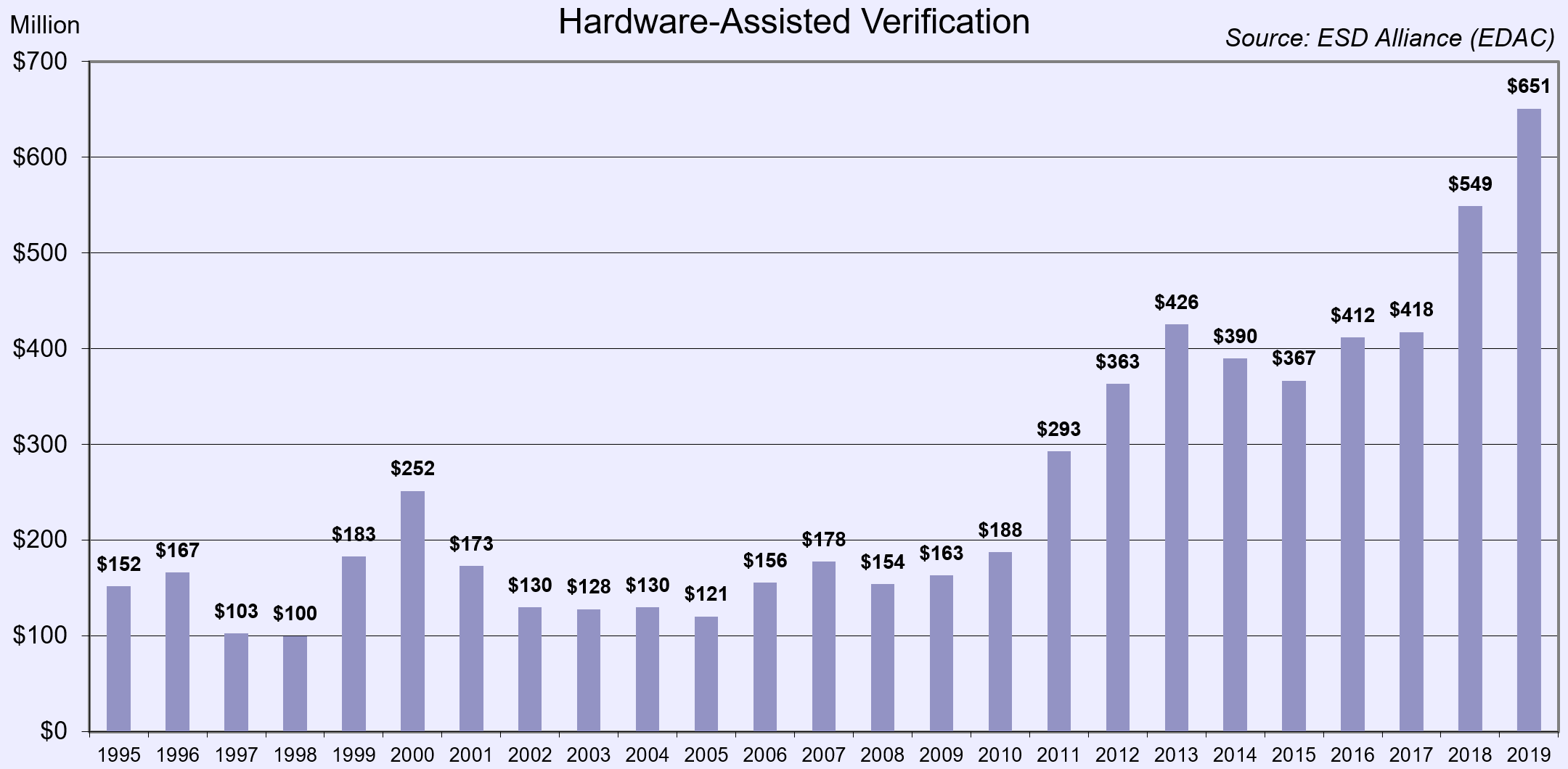

Emulation can accelerate design verification of any design, irrespective of type and size. Especially for leading-edge segments of the electronic industry creating designs for 5G, Artificial Intelligence (AI) or Machine Learning (ML) & autonomous driving vehicle applications that typically excel in dimensions and complexity. This article throws light on the future of emulation and how hardware emulation outshines any other verification tool with an impressive variety of use models, for a multitude of verification tasks, & virtually limitless applications.

Emulation can accelerate design verification of any design, irrespective of type and size. Especially for leading-edge segments of the electronic industry creating designs for 5G, Artificial Intelligence (AI) or Machine Learning (ML) & autonomous driving vehicle applications that typically excel in dimensions and complexity. This article throws light on the future of emulation and how hardware emulation outshines any other verification tool with an impressive variety of use models, for a multitude of verification tasks, & virtually limitless applications.