Article Roundup: Training novel NVM non determinism, High Level Synthesis at the Edge, The ABCs of Functional Verification, Improving functional safety for ICs , Tessent awarded by Samsung, Tessent awarded by Samsung, Interview with Mentor’s Sagi Reuven: Business Practices Drive the Smart Factory, Not the Other Way Around.

- Taming novel NVM non determinism

- High Level Synthesis at the Edge

- Improving Functional Safety for ICs

- Tessent awarded by Samsung

- Interview with Mentor’s Sagi Reuven: Business Practices Drive the Smart Factory, Not the Other Way Around

Taming novel NVM non determinism

SemiEngineering

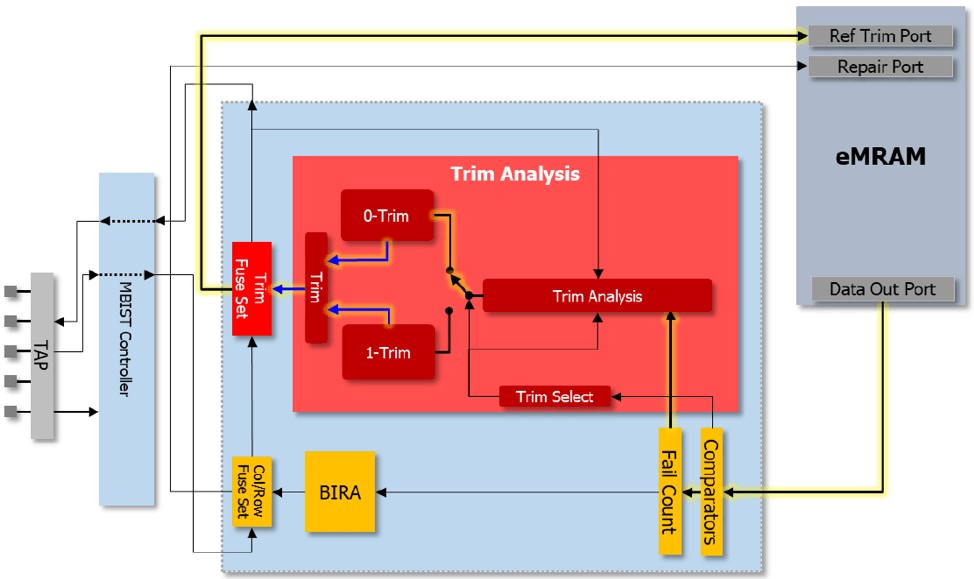

The Tessent Shell MBiST solution for SRAMs provides a fully automated flow from DFT planning, through DFT insertion, to pattern generation and validation. This article talks about how Mentor, Arm, and Samsung are collaborating on a project to develop the trimming capability as a part of the MRAM built-in self-test (BiST) function. Furthermore, DFT design flows have evolved to provide a highly automated way of inserting test circuitry.

High Level Synthesis at the Edge

SemiWiki

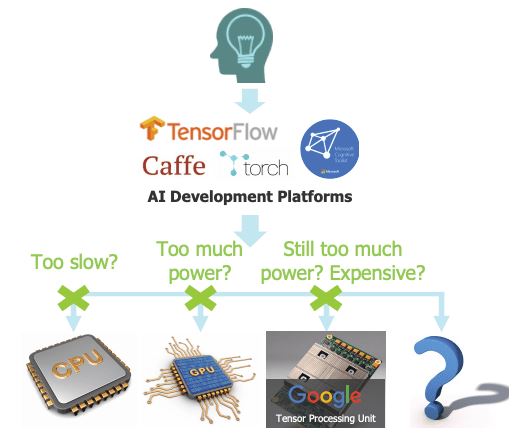

In this article, different methods of running the majority of testing in C rather than RTL is explored. Neural net algorithms map well, through high-level synthesis (HLS), so the C model can be more than a model – it can be the implementation from which the designer can generate the RTL and explore the power, performance and area implications of choices and more.

Improving Functional Safety for ICs

SemiEngineering

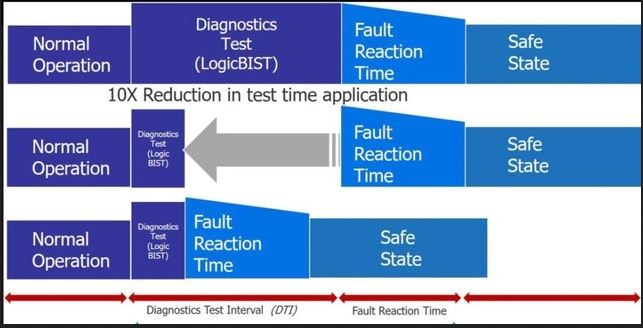

LBIST-OST technology leverages test points to reduce the DTTI by increasing the fault detection period, delivering up to 10x faster in-system test than traditional LBIST and reduces the number of test patterns needed.

This article throws light on how designers can reduce in-system test time (DTTI) and area overhead using LBIST-OST. Another important facet is that Observation scan completes tests faster, thereby simplifying key-on, key-off, and periodic checkups during functional operation.

Tessent awarded by Samsung

MentorBlogs

In recognition of the value of the collaboration with Tessent, specifically in the development of advanced hierarchical DFT, Samsung presented the Tessent group with their SAFE™ (Samsung Advanced Foundry Ecosystem) award for Best Collaboration of 2019. This blog highlights the proven divide-and-conquer approach to lowering test time and enabling faster time-to-market. It allows all DFT and ATPG work to be completed at the core/block level, which keeps DFT out of the critical path to tapeout and can reduce implementation time by 50% compared to flat DFT flows.

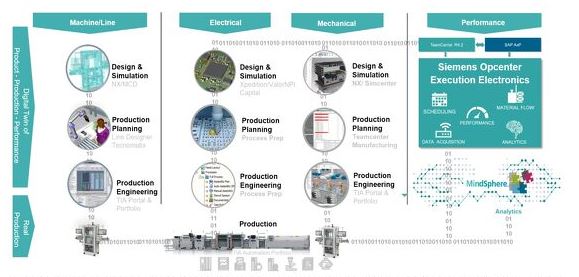

Industry 4.0 is not about connecting another machine and collecting data; it is about the mindset of understanding that solution of most problems. This article, the author explains how the system extends through the entire electronics value chain, including PCB, mechanical & box build processes. Mentor’s Sagi Reuven also covers how sometimes the key to utilizing Industry 4.0 comes from a change or investment in new equipment or provesses.

Industry 4.0 is not about connecting another machine and collecting data; it is about the mindset of understanding that solution of most problems. This article, the author explains how the system extends through the entire electronics value chain, including PCB, mechanical & box build processes. Mentor’s Sagi Reuven also covers how sometimes the key to utilizing Industry 4.0 comes from a change or investment in new equipment or provesses.