Article Roundup: EDA In the Cloud, How to Become an RTL Simulation Expert vs Hardware Emulation Expert, Multicore systems: heterogeneous architectures – untangling the technology and terminology, Earlier is Better In Latch-Up Detection, Right-first-time PCB layout for spacecraft avionics

- How to Become an RTL Simulation Expert vs. Hardware Emulation Expert

- Multicore systems: heterogeneous architectures – untangling the technology and terminology

- Earlier Is Better In Latch-Up Detection

- Right-first-time PCB layout for spacecraft avionics

- EDA In The Cloud

How to Become an RTL Simulation Expert vs. Hardware Emulation Expert

ElectronicDesign

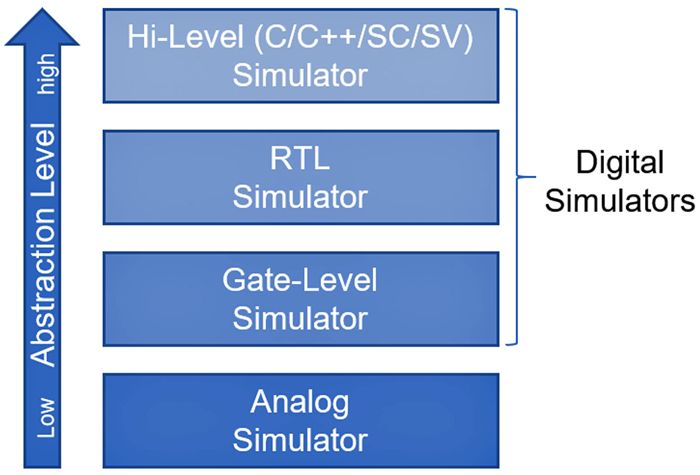

Hardware emulation is a mandatory design-verification tool. In this part of the two-part series, the author highlights that all simulators above analog are digital and they process the DUT at increasingly higher abstraction levels than transistor analog voltages and current, from gate level to RTL. Furthermore, the requirements to become a RTL simulation expert & an Emulation expert is discussed in detail in this article.

Multicore systems: heterogenous architectures – untangling the technology and terminology

EdaCafe

Mentor’s Colin Walls, throws light about the different facets of multicore design that includes configuration, debugging and how a developer needs to have a view of the system as a whole. He further explains that SMP architecture has its uses in the world of embedded systems with a number of real-time operating systems including NucleusOS.

Mentor’s Colin Walls, throws light about the different facets of multicore design that includes configuration, debugging and how a developer needs to have a view of the system as a whole. He further explains that SMP architecture has its uses in the world of embedded systems with a number of real-time operating systems including NucleusOS.

Earlier Is Better In Latch-Up Detection

SemiEngineering

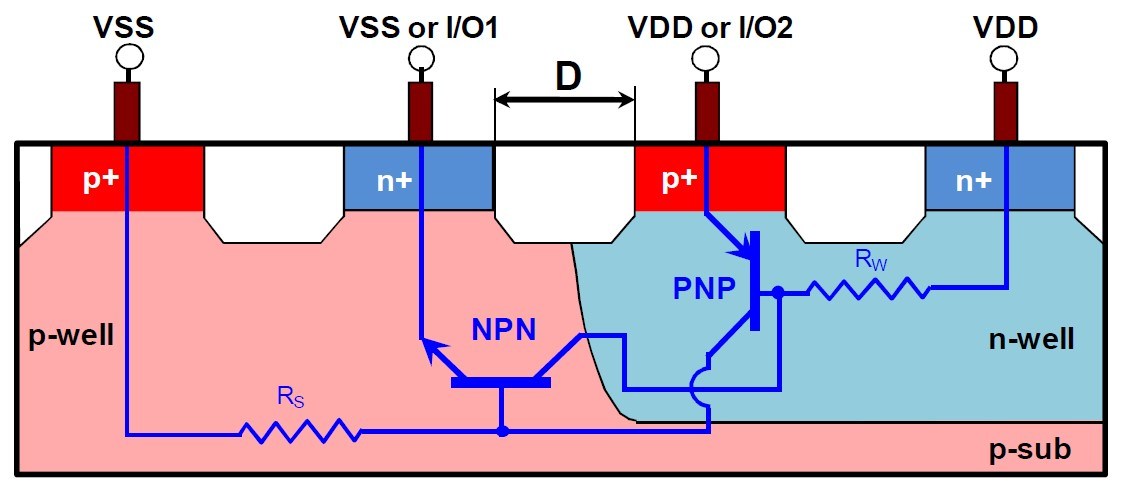

Traditional latch-up detection occurs late in the design flow, requiring costly and time-consuming late-stage physical layout changes. By running automated topology-based latch-up verification on the schematic netlist during early design phases, designers can quickly identify sensitive latch-up scenarios. Most of these latch-up conditions can be quickly resolved through circuit design changes without any major impact on IC implementation, preventing expensive delays and emergency rerouting. This article explains the methodologies and need of traditional latch-up protection, spacing protection, guard ring protection, topology-driven latch-up protection and more

Traditional latch-up detection occurs late in the design flow, requiring costly and time-consuming late-stage physical layout changes. By running automated topology-based latch-up verification on the schematic netlist during early design phases, designers can quickly identify sensitive latch-up scenarios. Most of these latch-up conditions can be quickly resolved through circuit design changes without any major impact on IC implementation, preventing expensive delays and emergency rerouting. This article explains the methodologies and need of traditional latch-up protection, spacing protection, guard ring protection, topology-driven latch-up protection and more

Right-first-time PCB layout for spacecraft avionics

EDNAsia

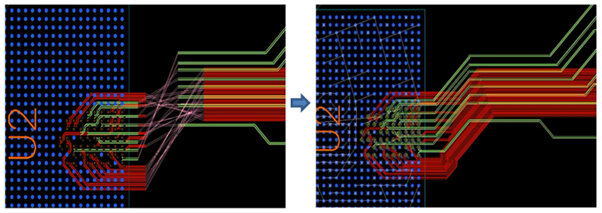

Mentor’s Xpedition suite allows the designer to create a virtual stack containing the required number of layers, quickly which can then be experimented with dielectric materials to optimize the characteristic impedance by adjusting permittivity, trace width, clearance, thickness, and separation for differential pairs amongst many other factors. This article talks about the fundamentality of PCB and how satellite & spacecraft avionics are increasingly combining K-band RF, GSPS analog and more into a single IC chip.

Mentor’s Xpedition suite allows the designer to create a virtual stack containing the required number of layers, quickly which can then be experimented with dielectric materials to optimize the characteristic impedance by adjusting permittivity, trace width, clearance, thickness, and separation for differential pairs amongst many other factors. This article talks about the fundamentality of PCB and how satellite & spacecraft avionics are increasingly combining K-band RF, GSPS analog and more into a single IC chip.

EDA In The Cloud

SemiEngineering

This video article discusses the growing compute requirements at 7, 5 and 3nm and more on why the cloud looks increasingly attractive from a security and capacity standpoint. The author also talk about how the cloud as well as new lithography will affect the cost and complexity of developing new chips.