Article Roundup: Catch latch-up earlier with schematic topology-based analysis, Toward more efficient formal strategies for deadlock, Balancing Flexibility and quality in SRAM Verification, It’s The Small Stuff That Gets You…, Clock-domain crossing protocols: an automated formal-to-simulation flow

- Catch latch-up earlier with schematic topology-based analysis

- Toward more efficient formal strategies for deadlock

- Balancing Flexibility And Quality In SRAM Verification

- It’s The Small Stuff That Gets You …

- Clock-domain crossing protocols: an automated formal-to-simulation flow

Catch latch-up earlier with schematic topology-based analysis

TechDesignForum

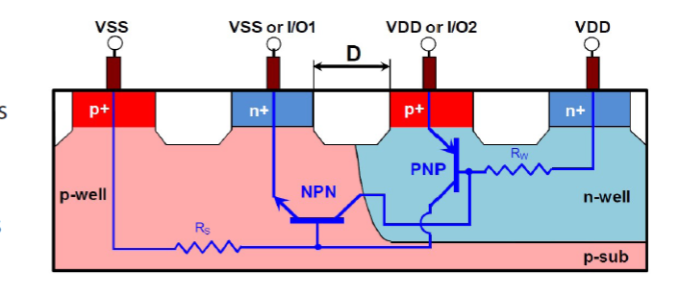

The need for high-reliability components is ever-present and growing across all of today’s market segments. By running Mentor’s reliability platform, designers can quickly identify latch-up sensitive scenarios through topological analysis. Latch up scenarios can then be resolved through circuit design changes without any major impact on IC implementation, preventing expensive delays and emergency rerouting. This article talks about automated analysis and the need to identify latch-up sensitive scenarios quickly.

The need for high-reliability components is ever-present and growing across all of today’s market segments. By running Mentor’s reliability platform, designers can quickly identify latch-up sensitive scenarios through topological analysis. Latch up scenarios can then be resolved through circuit design changes without any major impact on IC implementation, preventing expensive delays and emergency rerouting. This article talks about automated analysis and the need to identify latch-up sensitive scenarios quickly.

Toward more efficient formal strategies for deadlock

TechDesignForum

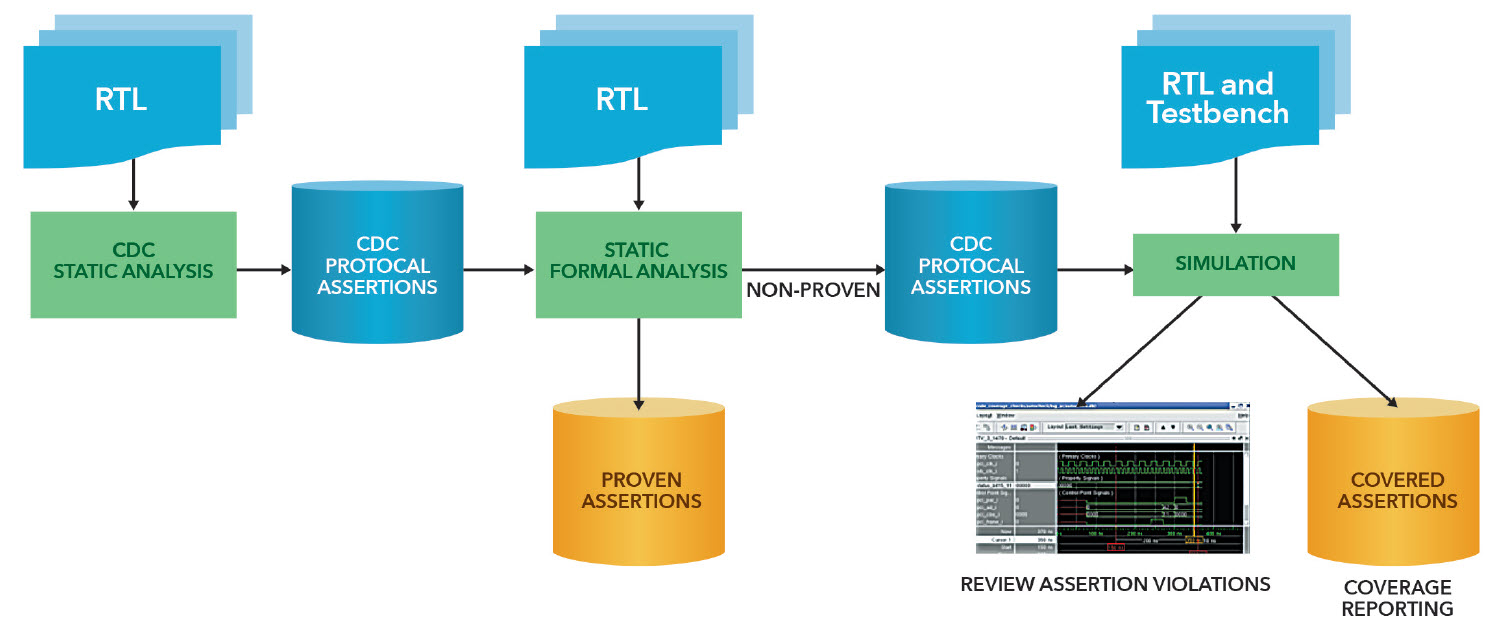

Formal verification tools develop a mathematical model of a given DUT, enabling formal analysis to exhaustively verify all inputs and outputs against the expected behaviors of all the states in a DUT, for all time. The formal analysis finds the deadlock traps relatively fast despite some constraints that are missing, the formal tool can generate some sort of illegal error condition and cause a reset. But, once the designer has constrained away the behaviors that they don’t want the analysis to consider, the tool will be single-mindedly focused on finding true system deadlock. This article describes a work flow that builds upon deadlock properties from SVA to incorporate the algorithms with safety objectives.

Formal verification tools develop a mathematical model of a given DUT, enabling formal analysis to exhaustively verify all inputs and outputs against the expected behaviors of all the states in a DUT, for all time. The formal analysis finds the deadlock traps relatively fast despite some constraints that are missing, the formal tool can generate some sort of illegal error condition and cause a reset. But, once the designer has constrained away the behaviors that they don’t want the analysis to consider, the tool will be single-mindedly focused on finding true system deadlock. This article describes a work flow that builds upon deadlock properties from SVA to incorporate the algorithms with safety objectives.

Balancing Flexibility and Quality in SRAM Verification

SemiEngineering

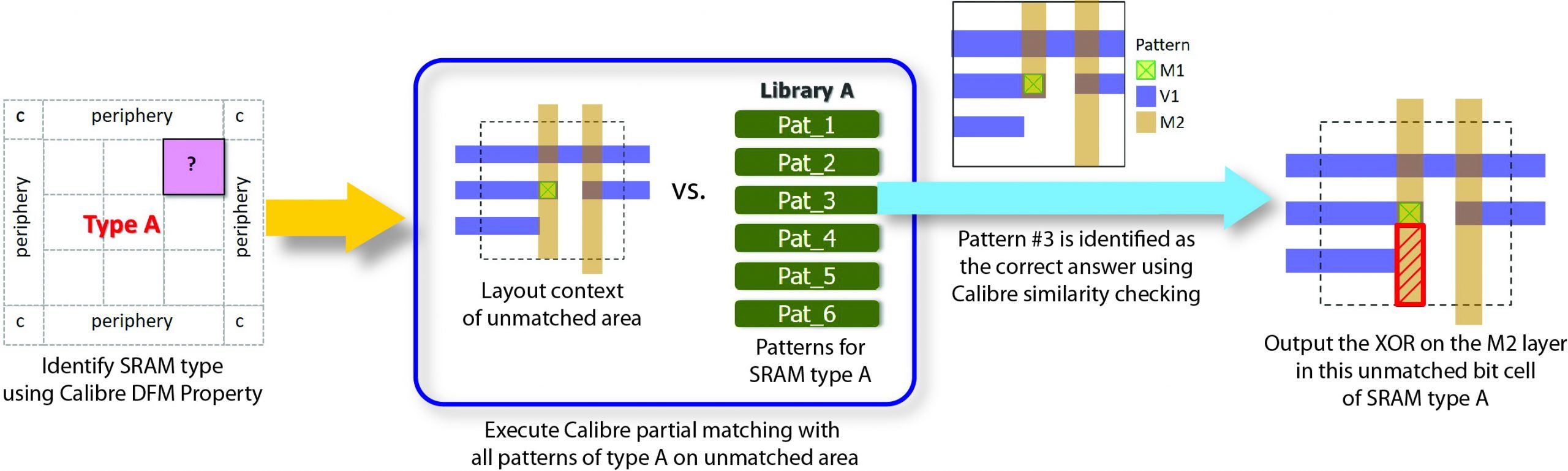

By finding and debugging SRAM modification errors efficiently, designers must have access to the information that enables them to quickly and precisely locate an SRAM error and determine the correct fix. By enhancing their SRAM verification and debugging process with automated pattern matching and similarity checking processes, SRAM designers can find a better, more precise balance between the design flexibility they need and the yield that market success requires. This article discusses SRAM verification challenges, pattern matching verification and the ideal flow to incorporate tolerances into SRAM verification rule check.

It’s the Small Stuff That Gets You …

SemiWiki

In any given high-speed, high-performance PCB design, there are areas of concern from a signal integrity perspective. The areas where crosstalk and coupling are likely to be an issue get close attention from the SI experts with a lot of tools and complexity prevalent in this part of the design process. This article talks about the interaction with Mentor’s Todd Westerhoff and his observations about the way high-performance PCBs could be designed.

Clock-domain crossing protocols: an automated formal-to-simulation flow

TechDesignForum

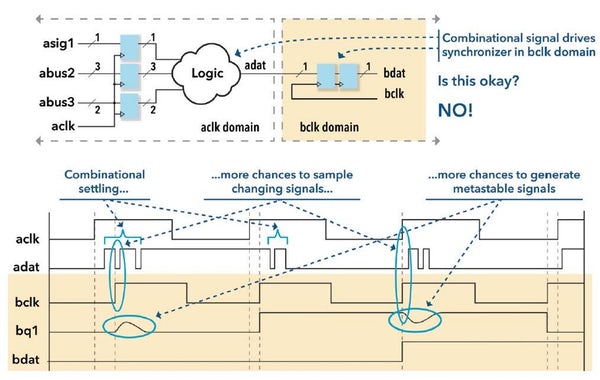

Automation reduces the time and errors of manual scripting & this approach improves debug productivity by correlating structural analysis, formal verification, and simulation results. This article talks about the systematic CDC protocol verification solution and how it improves the accuracy of formal analysis by reducing false formal firings that allows the designer to debug and fix protocol errors more quickly and with less effort.

Automation reduces the time and errors of manual scripting & this approach improves debug productivity by correlating structural analysis, formal verification, and simulation results. This article talks about the systematic CDC protocol verification solution and how it improves the accuracy of formal analysis by reducing false formal firings that allows the designer to debug and fix protocol errors more quickly and with less effort.