Article Roundup: AI/ML at DVCON: From Theory to Application, Bringing Hierarchy to DFT, Formal Flow for Automotive Safety, Todd Westerhoff on the value of Solid Design skills, Siemens develops validation program to accelerate AV development

- AI/ML at DVCon: From Theory to Application

- Bringing Hierarchy to DFT

- Formal Flow for Automotive Safety

- Todd Westerhoff on the Value of Solid Design Skills

- Siemens develops validation program to accelerate AV development

AI/ML at DVCon: From Theory to Application

MentorBlogs

The interest in AI/ML solutions has moved beyond the bounds of research and has become a key component within many of today’s designs—ranging from voice and image recognition, near-real-time fraud detection, as well as optimize spectrum bandwidth dynamically for efficient 5G operation.

This year’s DVCON will cover interesting tutorials that takes the user through the process of migrating an algorithm from generic software to a hardware implementation, tools & solutions including simulation, emulation, High-Level Synthesis and more.

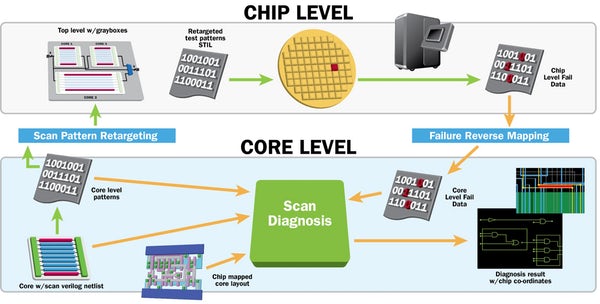

Bringing Hierarchy to DFT

SemiWiki

Mentor is on the leading edge of the move to hierarchical Design for Test (DFT), a part of the flow that has for many years resisted switching from a predominantly flat approach. This article highlights the role of clocking in DFT and how Mentor’s Tessent products allow exploration and utilization of existing registers for use during test. By taking a divide-and-conquer approach to test, various challenges such as long DFT implementation and ATPG runtimes can be solved.

Mentor is on the leading edge of the move to hierarchical Design for Test (DFT), a part of the flow that has for many years resisted switching from a predominantly flat approach. This article highlights the role of clocking in DFT and how Mentor’s Tessent products allow exploration and utilization of existing registers for use during test. By taking a divide-and-conquer approach to test, various challenges such as long DFT implementation and ATPG runtimes can be solved.

Formal Flow for Automotive Safety

CircuitCellar

The ISO 26262 automotive functional safety standard requires executing random hardware failure analysis of electronic devices for automotive applications. This article emphasizes that Formal tools can prove that a fault is safe or latent & can quickly determine a worst-case/best-case diagnostic coverage without time-consuming analysis. This article also presents an improved formal verification flow that uses sequential logic equivalency checking (SLEC) to reduce the number of faults while simultaneously providing much higher quality of results.

Todd Westerhoff on the Value of Solid Design Skills

iConnect007

Design reviews take significant time and effort, but they are quicker and less resource-intensive than full-scale modeling and simulation. Running a design review requires check-pointing the design, sending something out for review, and waiting for people to review the material, and then pulling all that feedback together. In this article, Todd Westerhoff discusses the reasons for good design skills to be more influential on a PCB than any software tool.

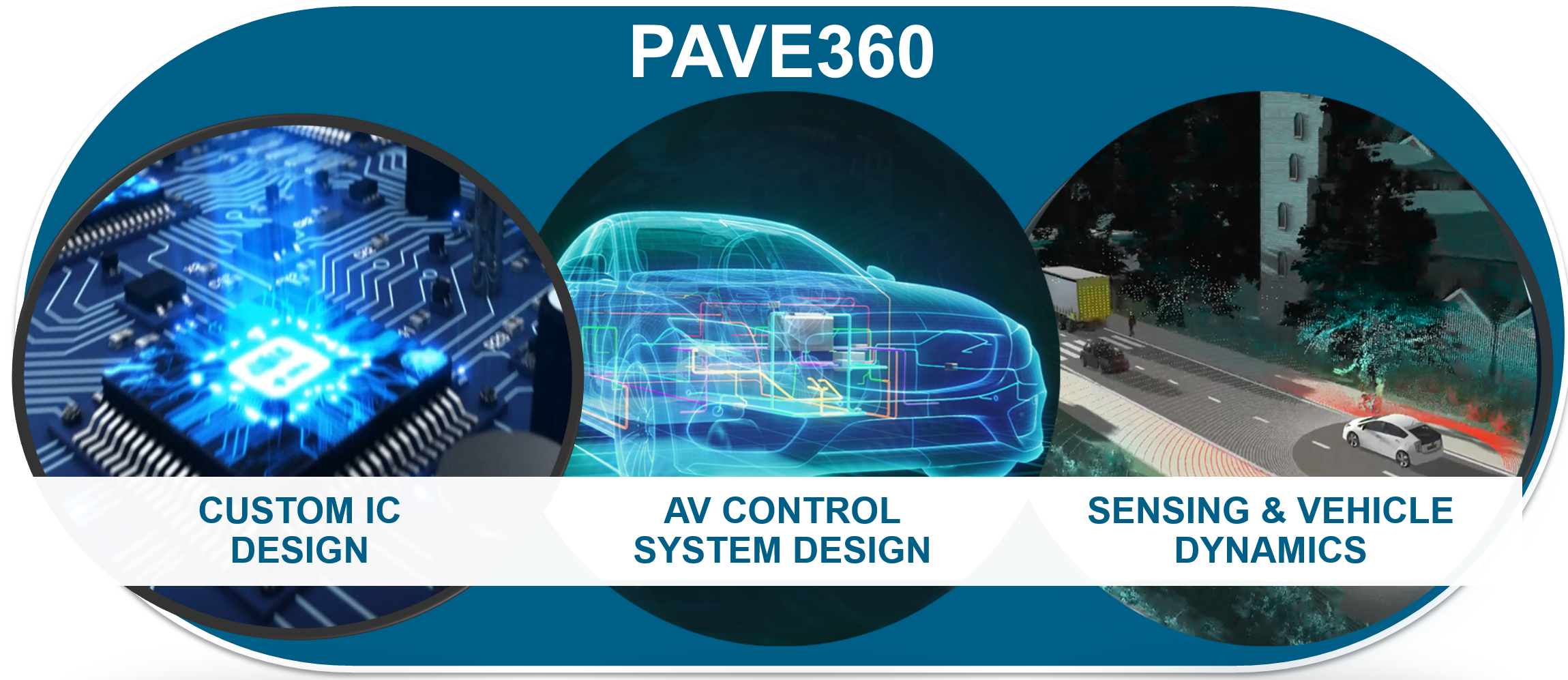

Siemens develops validation program to accelerate AV development

AutonomousVehicleTech

The combination of Siemens and Mentor employees and their ideas supports the deep, cross-ecosystem collaboration necessary for its customers to develop powerful custom IC and software solutions for the AV revolution. By developing the PAVE360 pre=silicon validation environment, it establishes a design-simulation-emulation solution that scales from individual blocks of a system-on-chip IP to vehicle subsystems – which increases digitalization of the automotive industry.

The combination of Siemens and Mentor employees and their ideas supports the deep, cross-ecosystem collaboration necessary for its customers to develop powerful custom IC and software solutions for the AV revolution. By developing the PAVE360 pre=silicon validation environment, it establishes a design-simulation-emulation solution that scales from individual blocks of a system-on-chip IP to vehicle subsystems – which increases digitalization of the automotive industry.