Article Roundup: Low-Power Memory, How to Pick an Embedded Processor, DFT for AI, MindSphere Oddities & Optimizing in the Age of Safety and Security

- Boost your DFT efficiency for AI silicon design

- Target: 50% Reduction In Memory Power

- What Processor Should I Use?

- Offbeat Siemens Customers Highlight MindSphere Functionality

- Optimization Challenges For Safety And Security

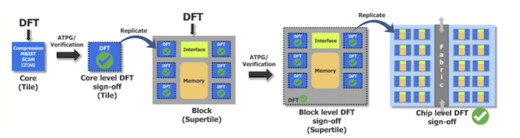

Boost your DFT efficiency for AI silicon design

Tech Design Forum

As the artificial intelligence market heats up, the pressure on teams to reduce the time and resources required for all stages of the design flow is climbing. This article looks at three strategies that design-for-test (DFT) engineers can use to achieve these reductions: exploiting AI chip regularity, performing DFT insertion at RTL, and eliminating DFT-to-test insertions.

As the artificial intelligence market heats up, the pressure on teams to reduce the time and resources required for all stages of the design flow is climbing. This article looks at three strategies that design-for-test (DFT) engineers can use to achieve these reductions: exploiting AI chip regularity, performing DFT insertion at RTL, and eliminating DFT-to-test insertions.

Target: 50% Reduction In Memory Power

SemiEngineering

Memory currently consumes around half of the area and power of an SoC, but these are both likely to increase. The culprit is static random access memory (SRAM) that has not scaled in line with Moore’s Law. Reducing the power consumption of memory is possible, but requires more than clever engineering to achieve targeted power savings of fifty percent.

What Processor Should I Use?

Embedded.com

In embedded system design, hardware and software development are linked inextricably. In this article, Colin Walls examines how software issues affect CPU selection for embedded systems. While there are obvious considerations, such as computing power, additional concerns include the software team’s familiarity with the CPU architecture and the availability of needed development tools.

Offbeat Siemens Customers Highlight MindSphere Functionality

IoT World Today

Imagine a parking garage that stores and retrieves vehicles automatically, or using the digital twin to model and improve wave machines for surfers, or the ability to design your dream car in virtual reality. These varied applications of digital engineering have one thing in common: Siemens Mindsphere. The IoT platform is just beginning to show the breadth of its capabilities as users continue to find new and interesting applications.

Imagine a parking garage that stores and retrieves vehicles automatically, or using the digital twin to model and improve wave machines for surfers, or the ability to design your dream car in virtual reality. These varied applications of digital engineering have one thing in common: Siemens Mindsphere. The IoT platform is just beginning to show the breadth of its capabilities as users continue to find new and interesting applications.

Optimization Challenges For Safety And Security

SemiEngineering

The tradeoffs between power, performance, and area (PPA) are becoming less clear as IC complexity increases. New safety and security requirements only compound this problem by adding additional variables to the PPA equation. What’s more, the industry is at different stages in the development of tool flows for each of these critical design variables. Solutions, however, are on the way as EDA vendors engage with domain experts to incorporate needed functionality into new tools.

The tradeoffs between power, performance, and area (PPA) are becoming less clear as IC complexity increases. New safety and security requirements only compound this problem by adding additional variables to the PPA equation. What’s more, the industry is at different stages in the development of tool flows for each of these critical design variables. Solutions, however, are on the way as EDA vendors engage with domain experts to incorporate needed functionality into new tools.