Article Roundup: Quickly Merging SoC Layouts, Blockchain for IIoT Security, Verifying 1st Gen AVs, Lua & Automating Analog Design Checking!

- Fast, accurate layout merging for SoC flows

- Blockchain May Be Overkill For Most IIoT Security

- Paving the Way to Verify and Validate the Design of First-Generation Automated Driving Vehicles

- Ah! Lua

- Automated Analog Design Constraint Checking

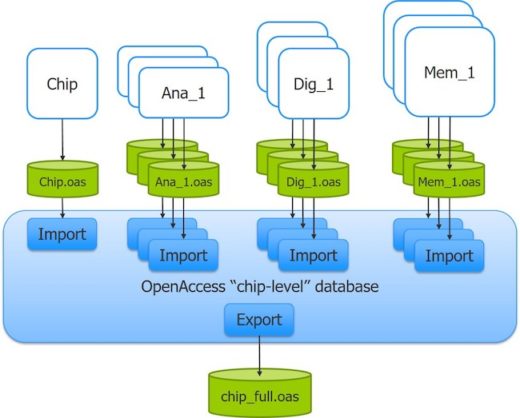

Fast, accurate layout merging for SoC flows

Tech Design Forum

SoC design teams run full-chip design rule checking (DRC) several times during the implementation process to catch violations between block instances early. This practice requires the team to assemble the latest physical layout data from a number of formats, and merge it into a single OASIS or GDSII database. This article describes a method that accelerates the merging of layout data, fast-tracking full-chip verification.

SoC design teams run full-chip design rule checking (DRC) several times during the implementation process to catch violations between block instances early. This practice requires the team to assemble the latest physical layout data from a number of formats, and merge it into a single OASIS or GDSII database. This article describes a method that accelerates the merging of layout data, fast-tracking full-chip verification.

Blockchain May Be Overkill For Most IIoT Security

SemiEngineering

Blockchain is touted as an ideal solution for securing IIoT-enabled industrial equipment. Several companies promote the technology as a means of tracing components, verifying sensor data, identifying devices, and more. But there are reasons to doubt the efficacy of blockchain for IIoT security, such as the sheer cost of implementing such a solution.

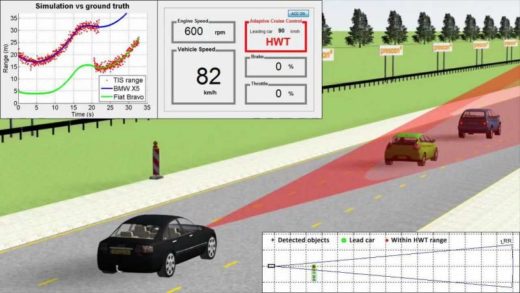

Paving the Way to Verify and Validate the Design of First-Generation Automated Driving Vehicles

Electronic Component News

As automotive OEMs race to claim their share of the autonomous vehicle market, ensuring the safety of the vehicles they develop will be a critical concern. This means exhaustively testing the many systems, that will enable automated driving, which could take decades to complete in the real world. These companies will need a virtual solution to effectively and efficiently test and verify their autonomous vehicle platforms.

As automotive OEMs race to claim their share of the autonomous vehicle market, ensuring the safety of the vehicles they develop will be a critical concern. This means exhaustively testing the many systems, that will enable automated driving, which could take decades to complete in the real world. These companies will need a virtual solution to effectively and efficiently test and verify their autonomous vehicle platforms.

Ah! Lua

EDACafé

Lua is a scripting language that runs by interpreting bytecode through a virtual machine. In this article, Colin Walls gives a brief overview of the language and explains why it might be useful for embedded software developers.

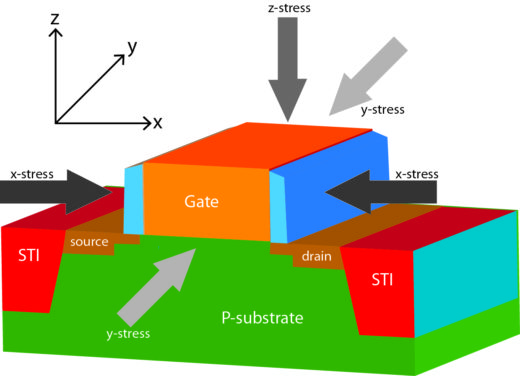

Automated Analog Design Constraint Checking

SemiEngineering

One of the main challenges of designing analog integrated circuits (IC) is achieving and maintaining accurate ratios for capacitors, resistors, current mirroring, and more. The performance and life expectancy of analog circuitry is sensitive to these ratios, so it is important that they remain consistent from design through manufacturing. Replacing error-prone manual inspections with automated constraint checking helps identify these and other subtle layout errors.

One of the main challenges of designing analog integrated circuits (IC) is achieving and maintaining accurate ratios for capacitors, resistors, current mirroring, and more. The performance and life expectancy of analog circuitry is sensitive to these ratios, so it is important that they remain consistent from design through manufacturing. Replacing error-prone manual inspections with automated constraint checking helps identify these and other subtle layout errors.