Article Roundup: Chip Industry Transition, DFT & Safety Emulation Apps, CMP Simulation, PSS-DSL & Correlating Rule-Based & Field Solver Parasitic Extraction Results

- Chip Industry In Rapid Transition

- Twin DFT and Mission-Critical Safety Apps for Pre-Silicon Design Verification

- Tackling Manufacturing Errors Early with CMP Simulation

- Why Mentor backs the PSS-DSL input format for the Portable Stimulus Specification

- Five Rules For Correlating Rule-Based And Field Solver Parasitic Extraction Results

Chip Industry In Rapid Transition

SemiEngineering

2018 was a year of change in the semiconductor industry, and the change is continuing in 2019. Wally Rhines, CEO Emeritus of Mentor, a Siemens Business, sat down with Ed Sperling, of Semiconductor Engineering, to discuss the changing industry. This article contains excerpts of their discussion, which ranges from fabless startups, AI, and memory to the impact of global economics on the semiconductor industry.

Twin DFT and Mission-Critical Safety Apps for Pre-Silicon Design Verification

Electronic Design

Design-for-test (DFT) technology sprung out of a need to limit the cost of testing chips. The insertion of DFT logic can compromise the integrity of the design, requiring the engineers to perform additional verification. Using simulation to perform this verification takes far too long because the inserted DFT logic significantly increases the size and complexity of the design. Mentor’s Veloce DFT App and Veloce Fault App combined with hardware emulation can accelerate DFT verification and increase fault coverage before tape-out.

Design-for-test (DFT) technology sprung out of a need to limit the cost of testing chips. The insertion of DFT logic can compromise the integrity of the design, requiring the engineers to perform additional verification. Using simulation to perform this verification takes far too long because the inserted DFT logic significantly increases the size and complexity of the design. Mentor’s Veloce DFT App and Veloce Fault App combined with hardware emulation can accelerate DFT verification and increase fault coverage before tape-out.

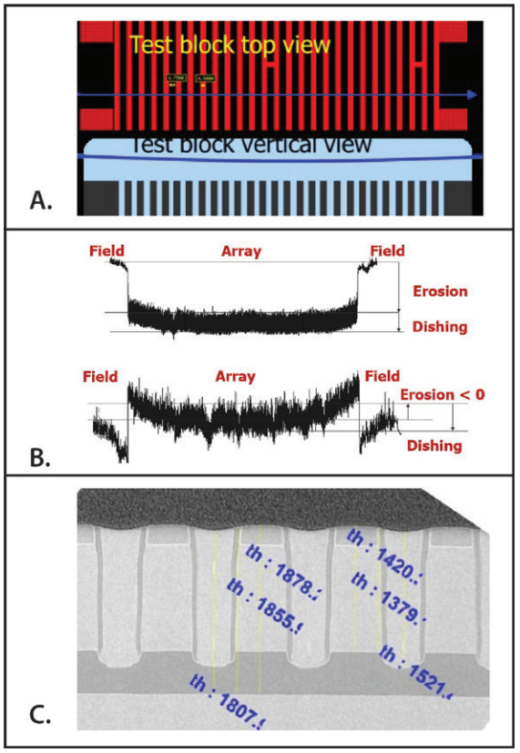

Tackling Manufacturing Errors Early with CMP Simulation

SemiWiki

Chemical mechanical polishing (CMP) has become an enabling technology for the complex surface structures of advanced node ICs. However, challenges with inconsistent pattern density or post-CMP surface quality persist, reducing manufacturing yield. This article examines how CMP simulation before manufacturing can improve yield by enabling early estimations of process outcomes, and the opportunity to resolve potential problems.

Chemical mechanical polishing (CMP) has become an enabling technology for the complex surface structures of advanced node ICs. However, challenges with inconsistent pattern density or post-CMP surface quality persist, reducing manufacturing yield. This article examines how CMP simulation before manufacturing can improve yield by enabling early estimations of process outcomes, and the opportunity to resolve potential problems.

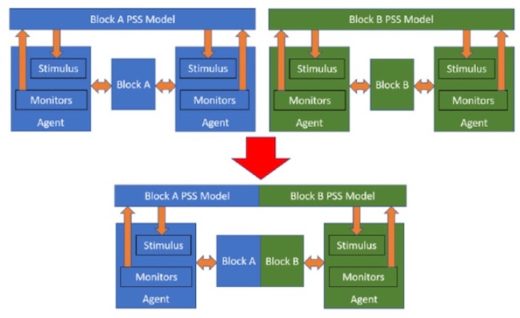

Why Mentor backs the PSS-DSL input format for the Portable Stimulus Specification

Tech Design Forum

The Portable Stimulus Specification (PSS) generates tests that can work across various verification environments to speed up the verification process. However, PSS still needed to incorporate two input formats to satisfy its wide range of users. In many cases, these formats can be mixed and matched as needed. When a choice does need to be made, Mentor recommends using the PSS-DSL format due to its conciseness & more accessible learning curve.

The Portable Stimulus Specification (PSS) generates tests that can work across various verification environments to speed up the verification process. However, PSS still needed to incorporate two input formats to satisfy its wide range of users. In many cases, these formats can be mixed and matched as needed. When a choice does need to be made, Mentor recommends using the PSS-DSL format due to its conciseness & more accessible learning curve.

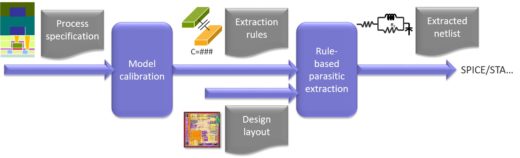

Five Rules For Correlating Rule-Based And Field Solver Parasitic Extraction Results

SemiEngineering

Eventually, every foundry and IC design company must run a correlation between a rule-based parasitic extraction table and a field solver solution. There are a number of common issues that can corrupt the comparison, producing an unfair conclusion. This article presents five modifications that may be required to calibrate each engine for fair and accurate comparisons.

Eventually, every foundry and IC design company must run a correlation between a rule-based parasitic extraction table and a field solver solution. There are a number of common issues that can corrupt the comparison, producing an unfair conclusion. This article presents five modifications that may be required to calibrate each engine for fair and accurate comparisons.

Comments

Leave a Reply

You must be logged in to post a comment.

In mentor graphics we are applying two inputs but how to apply phase shift to one input signal. Hope u have a solution for this.. thanking you sir.

What solution are you experiencing this issue with?