Article Roundup: Santa’s Autonomous Sleigh, Improving IC Yield Ramp, Silicon Photonics, Custom IC Design Management & HDAP Verification

- If Santa had an Autonomous Sleigh

- Layout schema generation: Improving yield ramp during technology development

- Realizing the Promise of Silicon Photonics

- Webinar: Tanner and ClioSoft Integration

- Adding system-level, post-layout electrical analysis to HDAP design and verification

If Santa had an Autonomous Sleigh

Siemens USA

Just because Santa can deliver presents to children around the world in under 24 hours on Christmas Eve doesn’t mean the process can’t be improved. In fact, this year Santa is investigating how autonomous driving technology can help increase the efficiency of his global gift delivery service. Read how Siemens’ portfolio of technologies can help Santa create a fleet of autonomous sleighs to make his holiday a little less taxing.

Just because Santa can deliver presents to children around the world in under 24 hours on Christmas Eve doesn’t mean the process can’t be improved. In fact, this year Santa is investigating how autonomous driving technology can help increase the efficiency of his global gift delivery service. Read how Siemens’ portfolio of technologies can help Santa create a fleet of autonomous sleighs to make his holiday a little less taxing.

Layout schema generation: Improving yield ramp during technology development

Solid State Technology

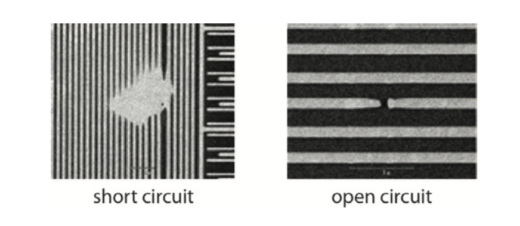

When creating a new IC technology, IC manufacturers usually use designs from a previous node to identify potential manufacturing failures. But, what do they do if a technology did not exist at the previous node? An innovative new technology, layout schema generation (LSG), enables design teams to generate additional macros to add to test structures without relying on past designs for input.

When creating a new IC technology, IC manufacturers usually use designs from a previous node to identify potential manufacturing failures. But, what do they do if a technology did not exist at the previous node? An innovative new technology, layout schema generation (LSG), enables design teams to generate additional macros to add to test structures without relying on past designs for input.

Realizing the Promise of Silicon Photonics

Photonics Media

Silicon photonics provide a number of significant benefits over traditional silicon ICs including transmission speed, low power, older proven processes, and more. So, why haven’t they taken over the market yet? Mentor’s John Ferguson examines how the slowing of Moore’s Law may give silicon photonics an opportunity, and the infrastructure they will need to capitalize.

Silicon photonics provide a number of significant benefits over traditional silicon ICs including transmission speed, low power, older proven processes, and more. So, why haven’t they taken over the market yet? Mentor’s John Ferguson examines how the slowing of Moore’s Law may give silicon photonics an opportunity, and the infrastructure they will need to capitalize.

Webinar: Tanner and ClioSoft Integration

SemiWiki

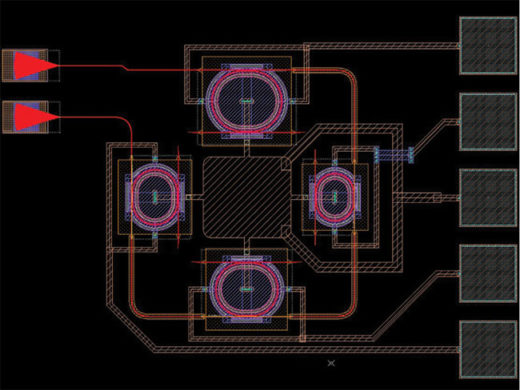

Mixed-signal ICs fuse digital and analog circuitry to enable bi-directional signal conversion from audial, temperature, and visual inputs to digital signals for processing. Mixed-signal designers often face shorter design cycles, making effective team collaboration critical to their success. To help these designers meet tight timelines, Tanner has integrated ClioSoft’s SOS7 design management solution to enable efficient local and multi-site collaboration.

Adding system-level, post-layout electrical analysis to HDAP design and verification

Tech Design Forum

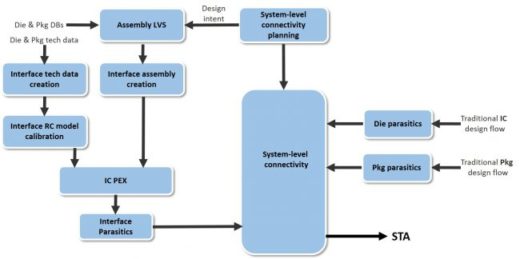

High-density advanced packaging offerings are expanding, but will require a more robust and standardized EDA flow to reach their full commercial potential. Current physical verification methods are a valuable starting point, but a more comprehensive flow that performs system-level electrical analysis is needed. This article describes what such a flow may look like, and what tools it will need.

High-density advanced packaging offerings are expanding, but will require a more robust and standardized EDA flow to reach their full commercial potential. Current physical verification methods are a valuable starting point, but a more comprehensive flow that performs system-level electrical analysis is needed. This article describes what such a flow may look like, and what tools it will need.