Article Roundup: AI and Domain Specific Chips, Automotive Design Safety, Reducing PCB Re-Spins, Emulation for Networking & Improving Gate-Level Simulation Throughput

- AI and the Domain Specific Architecture

- Adding Safety Into Automotive Design

- Shift Left for Fewer PCB Re-Spins

- Maximizing hardware emulation’s value for networking designs

- How to improve throughput for gate-level simulation

AI and the Domain Specific Architecture

SemiWiki

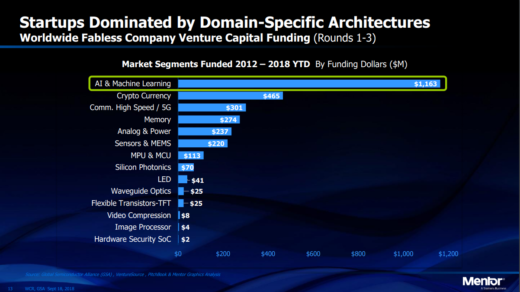

In a recent Keynote, Wally Rhines addressed the recent growth in the semiconductor industry. Domain-specific chip designs, especially those for artificial intelligence, are a large contributor to this growth as funding for fabless startups has skyrocketed. With interest in AI at a high, semiconductor growth may continue, but for how long?

In a recent Keynote, Wally Rhines addressed the recent growth in the semiconductor industry. Domain-specific chip designs, especially those for artificial intelligence, are a large contributor to this growth as funding for fabless startups has skyrocketed. With interest in AI at a high, semiconductor growth may continue, but for how long?

Adding Safety Into Automotive Design

SemiEngineering

ISO 26262 is causing a shift in the automotive design process as more components are being brought under its governance. Modern vehicle systems are increasingly realized electronically through sensors, actuators, and a variety of integrated circuits. These new systems must be designed for safety from the very beginning and meet requirements at the part, system, and platform levels.

Shift Left for Fewer PCB Re-Spins

EE Journal

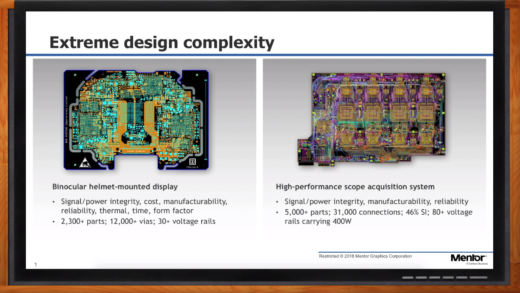

Today’s PCB designs are growing in complexity to enable increasingly sophisticated electronic products. Design rule checking (DRC) is becoming more important as design errors become harder to identify and resolve manually. New advanced design tools enable engineers to perform DRC earlier in the design process, eliminating costly re-spins and improving time-to-market.

Today’s PCB designs are growing in complexity to enable increasingly sophisticated electronic products. Design rule checking (DRC) is becoming more important as design errors become harder to identify and resolve manually. New advanced design tools enable engineers to perform DRC earlier in the design process, eliminating costly re-spins and improving time-to-market.

Maximizing hardware emulation’s value for networking designs

EDN Network

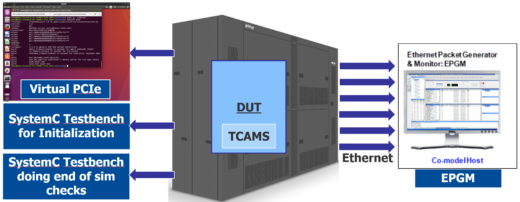

Designing an ASIC for networking applications comes with unique challenges, such as needing considerably more simulation cycles to complete bandwidth and latency testing. These challenges slow the design process and increase the cost of developing networking chips. Read how Cisco adopted a combined simulation and emulation methodology to improve the verification of these chips.

Designing an ASIC for networking applications comes with unique challenges, such as needing considerably more simulation cycles to complete bandwidth and latency testing. These challenges slow the design process and increase the cost of developing networking chips. Read how Cisco adopted a combined simulation and emulation methodology to improve the verification of these chips.

How to improve throughput for gate-level simulation

Tech Design Forum

Gate-level simulation continues to play a critical role in IC verification flows despite the increased complexity of today’s designs. For example, post-synthesis gate-level timing verification and DFT validation techniques that use automated test pattern generation (ATPG) both rely on simulation. This article discusses techniques for increasing the throughput of gate-level simulation to accelerate verification of today’s complex chips.

Gate-level simulation continues to play a critical role in IC verification flows despite the increased complexity of today’s designs. For example, post-synthesis gate-level timing verification and DFT validation techniques that use automated test pattern generation (ATPG) both rely on simulation. This article discusses techniques for increasing the throughput of gate-level simulation to accelerate verification of today’s complex chips.