Article Roundup: SSD Controller Emulation, IESF Automotive, Tool Interfaces, Verification Completion, HDAP

- What’s The Best Way to Verify Your SSD Controller?

- Gallery: Scenes at the Mentor Graphics Integrated Electrical Solutions Forum

- Why Open and Supported Interfaces Matter

- When Is Verification Complete?

- A Comprehensive High-Density Advanced Packaging Solution for Today’s OSATS and Foundries

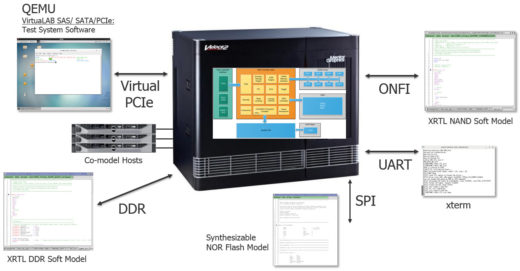

What’s The Best Way to Verify Your SSD Controller?

EETimes

ICE and virtual emulation methodologies are being adopted for full chip functional verification of SSD controller designs as well as the firmware. A virtual emulation methodology doesn’t require actual hardware peripherals, but instead uses models/software representations of the peripherals. Because there are no physical hardware connections, they can run the full system in a faster, more flexible configuration.

ICE and virtual emulation methodologies are being adopted for full chip functional verification of SSD controller designs as well as the firmware. A virtual emulation methodology doesn’t require actual hardware peripherals, but instead uses models/software representations of the peripherals. Because there are no physical hardware connections, they can run the full system in a faster, more flexible configuration.

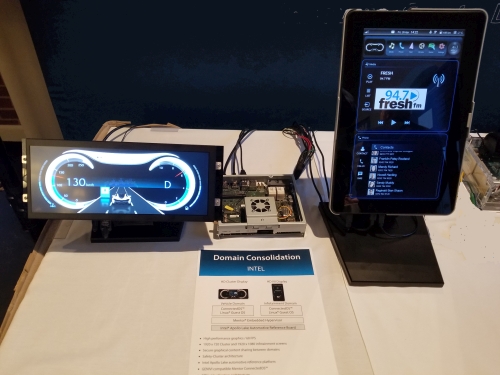

Gallery: Scenes at the Mentor Graphics Integrated Electrical Solutions Forum

Microcontroller Tips

IESF Automotive’s autonomous and connected vehicle themes provided nearly 800 attendees with a heavy dose of cutting-edge technology. Technology features included domain consolidation, AUTOSAR boards, automotive audio bus, solid-state LiDAR, security, and more. This article features sights seen from the event during technical sessions and in the solutions expo.

IESF Automotive’s autonomous and connected vehicle themes provided nearly 800 attendees with a heavy dose of cutting-edge technology. Technology features included domain consolidation, AUTOSAR boards, automotive audio bus, solid-state LiDAR, security, and more. This article features sights seen from the event during technical sessions and in the solutions expo.

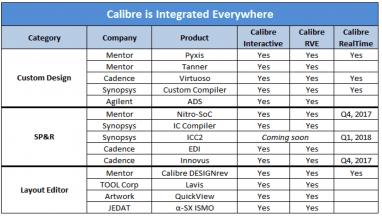

Why Open and Supported Interfaces Matter

SemiWiki

The lack of good interfaces between design tools can take up valuable engineering resources. Mentor offers the Calibre platform in multiple configurations to best suit the needs of a wide variety of customers, from small mixed-signal design consulting firms, to large digital SoC enterprises.

The lack of good interfaces between design tools can take up valuable engineering resources. Mentor offers the Calibre platform in multiple configurations to best suit the needs of a wide variety of customers, from small mixed-signal design consulting firms, to large digital SoC enterprises.

When Is Verification Complete?

Semiconductor Engineering

Verification experts, including our own Harry Foster, comment on deciding when verification is done. The increasingly difficult decision has prompted design teams to increase their reliability on metrics rather than just the test listed in the verification plan. This expert roundtable also features insights from the 2016 Wilson Research Group Functional Verification Study.

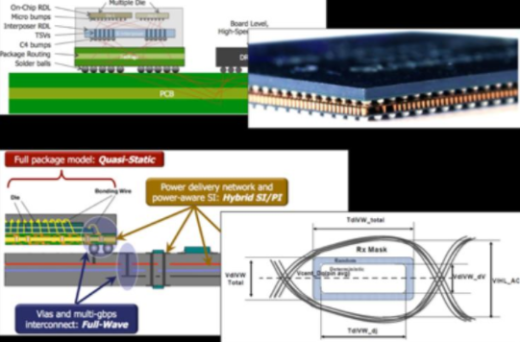

A Comprehensive High-Density Advanced Packaging Solution for Today’s OSATS and Foundries

Chip Scale Review

High density advanced packaging (HDAP) design and verification requires cooperation and collaboration between design houses, OSATS, foundries, and EDA vendors. With common tools that have the integration and functionality needed to operate in both the IC and packaging domains, companies can reduce turnaround time and the risk of package failure.

High density advanced packaging (HDAP) design and verification requires cooperation and collaboration between design houses, OSATS, foundries, and EDA vendors. With common tools that have the integration and functionality needed to operate in both the IC and packaging domains, companies can reduce turnaround time and the risk of package failure.

Comments

Leave a Reply

You must be logged in to post a comment.

Thank you so much Expert Insights, for giving us such an amazing updates. I hope we will get more knowledgeable latest updates from you.