Top Articles: Wally Rhines Interview, High-Level Synthesis, DFM, Analog IP Verification, Portable Stimulus

- Executive Insight: Wally Rhines

- How HLS is Giving Shape to Glasses-Free 3DTV

- An Intelligent DFM Approach is Critical for Today’s Advanced PCB Manufacturing

- Project Management Tools for Analog IP Verification

- Portable Stimulus Status Report

Executive Insight: Wally Rhines

Semiconductor Engineering

Wally Rhines, president and CEO of Mentor, a Siemens Business, sat down to discuss industry consolidation, a shift in emphasis from chips to systems, and what the recent acquisition by Siemens will mean for Mentor. Also discussed were the next big challenges across technology, business, and ecosystems.

Wally Rhines, president and CEO of Mentor, a Siemens Business, sat down to discuss industry consolidation, a shift in emphasis from chips to systems, and what the recent acquisition by Siemens will mean for Mentor. Also discussed were the next big challenges across technology, business, and ecosystems.

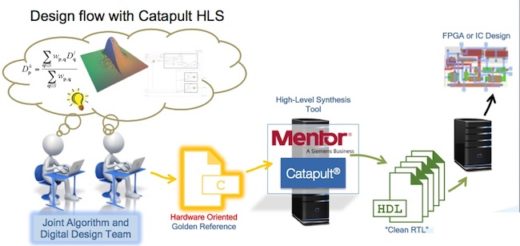

How HLS is Giving Shape to Glasses-Free 3DTV

Tech Design Forum

High level synthesis (HLS) has become a popular choice for algorithmic-intensive designs, such as video processing. When SeeCubic developed an HLS implementation strategy for their 3D-TVs, the overall development project was realized in half the time versus using a traditional flow.

High level synthesis (HLS) has become a popular choice for algorithmic-intensive designs, such as video processing. When SeeCubic developed an HLS implementation strategy for their 3D-TVs, the overall development project was realized in half the time versus using a traditional flow.

An Intelligent DFM Approach is Critical for Today’s Advanced PCB Manufacturing

EMS Now

Traditional design for manufacturing (DFM) methods are obsolete with today’s increasing complexity of printed circuit board (PCB) technology. The time is right in rethinking a better, more intelligent approach to DFM that addresses the complexities of analysis, management, and implementation.

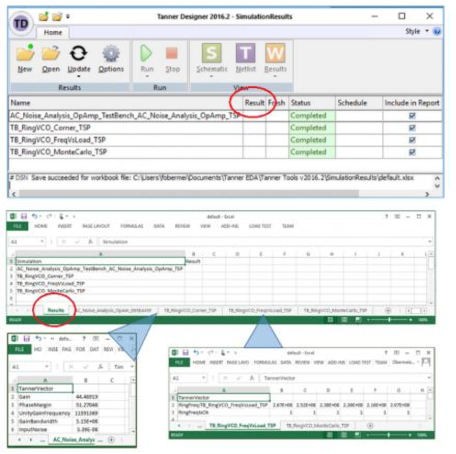

Project Management Tools for Analog IP Verification

SemiWiki

Analog/mixed-signal IP design teams often have limited infrastructure at their disposal for project management (PM). There has typically been little focus on tools and flows to assist with the PM tasks, or to establish a formal and consistent methodology for defining and reporting project status and specification pass/fall results. This article highlights Tanner Designer, developed specifically to aid with analog verification project management.

Analog/mixed-signal IP design teams often have limited infrastructure at their disposal for project management (PM). There has typically been little focus on tools and flows to assist with the PM tasks, or to establish a formal and consistent methodology for defining and reporting project status and specification pass/fall results. This article highlights Tanner Designer, developed specifically to aid with analog verification project management.

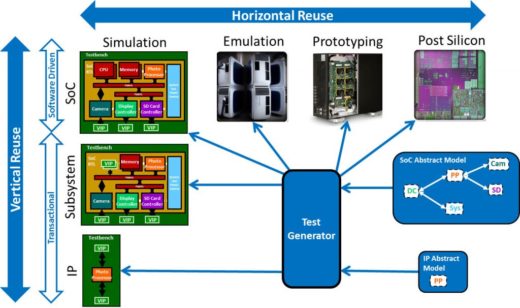

Portable Stimulus Status Report

Semiconductor Engineering

The Portable Stimulus (PS) standard’s first release is scheduled for early next year. If it lives up to its promise, it could be the first new language and abstraction for verification in two decades. Benefits include automation for generic, repetitive tasks, improved quality, and makes creating testcases at the system level much easier.

The Portable Stimulus (PS) standard’s first release is scheduled for early next year. If it lives up to its promise, it could be the first new language and abstraction for verification in two decades. Benefits include automation for generic, repetitive tasks, improved quality, and makes creating testcases at the system level much easier.