Verification and optimization of power delivery networks for AMD Versal devices

Power integrity has become a critical challenge for hardware designers in today’s high-performance computing landscape. This is particularly true for complex electronic systems utilizing advanced adaptive SoCs like AMD’s Versal™ family. While ensuring stable power delivery is paramount, overengineering power delivery networks (PDNs) can negatively impact product costs and time-to-market. This blog explores how Siemens HyperLynx™ PI tools help engineers optimize their PDN designs for both performance and cost-effectiveness.

Understanding the challenge

Modern adaptive SoCs require precise power delivery across a broad frequency spectrum, from DC to the gigahertz range. The PDN must maintain stable voltage levels while managing current transients and minimizing impedance across all frequencies. Traditional approaches often err on the side of caution, resulting in overdesigned solutions with excessive decoupling capacitors and unnecessary costs. Conversely, insufficient analysis can lead to missing issues in designs with power integrity vulnerabilities, which may require costly re-designs during prototyping or production.

A systematic approach to PDN optimization

Through collaboration between Siemens EDA and AMD, a comprehensive workflow was developed that enables designers to optimize their PDN designs systematically. The process begins with AMD’s Power Design Manager (PDM), which provides initial power requirements and decoupling recommendations based on the specific device’s configuration.

The workflow leverages the advanced capabilities of HyperLynx PI to:

- Accurately model the complete power delivery system, including the voltage regulator module (VRM), PCB planes, and decoupling capacitors

- Analyze PDN performance against target impedance requirements

- Optimize decoupling capacitor selection and placement using a genetic algorithm, which evolves the design through multiple iterations, improving potential design variants with each generation.

Real-world results

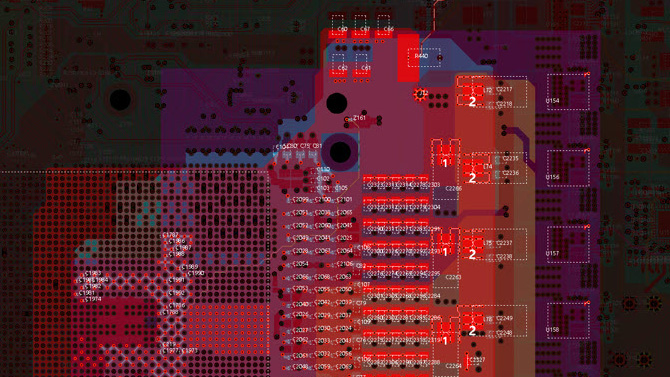

In a case study involving the AMD VCK190 evaluation board, the HyperLynx PDN Decoupling Optimizer demonstrated significant improvements:

- Reduction in decoupling capacitor count from 172 to 111 components

- Decreased variety of capacitor types from 7 to 6 distinct part numbers

- Parts cost reduction of nearly 30% with a slight improvement in performance margin

- Simplified board layout due to reduced component count

Business impact

These optimizations deliver several key business benefits:

- Reduced bill of materials costs

- Simplified component sourcing and inventory management

- Improved manufacturability through reduced component placement

- Lower risk of design iterations and associated delays

- More efficient use of board real estate

Looking forward

For engineering executives managing complex electronic product development, implementing an advanced PDN verification and optimization workflow offers a clear competitive advantage over traditional methods. The collaboration between Siemens and AMD demonstrates how modern EDA tools transform complex engineering challenges into tangible business value. As high-power ICs and adaptive SoCs continue to evolve, the ability to optimize PDN designs becomes increasingly crucial for maintaining competitive advantage in the market.

For design teams working with AMD Versal devices, this optimized workflow provides a clear path to achieving robust power integrity while achieving business goals. The combination of AMD’s device-specific models and Siemens’ HyperLynx PI tools enables engineers to make informed decisions that balance performance, cost, and design constraints effectively.

For more information on this topic, please read the white paper: Frequency-impedance verification of power delivery networks with HyperLynx PI for AMD Versal adaptive SoC devices.