Don’t Forget the Basics! Always Check for T-Fork Topology.

DDR memories allow the transfer of data at a higher speed than most other memory technologies. As the DDR technology gets cheaper, it is being used more frequently than ever before. Even devices in the small- and mid-market segments with tight budgets are utilizing the technology to create faster, smaller, and better products.

Does that mean we all have to become experts in DDR design and simulation? How can we make sure that we don’t make any mistakes in the design? With the HyperLynx® DRC starter editions, you can easily check for the basics of DDR design.

Today, let’s look at the T-fork topology DRC check. Admittedly, there is more to DDR design than making sure that the nets are balanced, yet the basics shouldn’t be forgotten.

T-fork topology is the most basic requirement in any design that works on a synchronized clock. It checks a net’s t-fork topology and its characteristics, including symmetrical forks, number of forks, and comparable fork lengths and trace widths

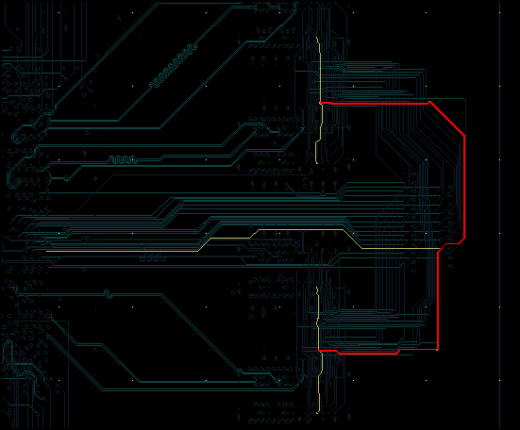

In HyperLynx DRC, simply type in the length tolerance and the number of branches you want to make sure are balanced. The tool will list all the violations, enabling you to click on each one to highlight the problem. For example, this screenshot clearly shows (highlighted above in red) that one branch is longer than the other and needs to be changed.

Feel free to try out this rule on your design, after all it’s free! Your free download starts here.

Comments

Leave a Reply

You must be logged in to post a comment.

Dear Ms Vaidya

I am interested in your offer HyperLynx DRC Gold Edition $995 is annually (12 months).

Is the price also valid for Czech Republic?

Can I order this tool at the link below?

https://www.mentor.com/pcb/hyperlynx/electrical-rule-check/drc-editions

Thank you for your interest in HyperLynx DRC. The pricing is the same everywhere including Czech Republic. Please use the same link to proceed with the purchase,during or after the download, feel free to post / browse on https://communities.mentor.com/community/pcb/hyperlynx/drc for more information.

Thanks

Kanchan Vaidya

Ladislav, is there anything we can do help you complete your order? Here is an easy link for making the purchase: https://www.mentor.com/promotions/get-drc.