SerDes Design Part 1: Take the First Steps Towards SerDes Channel Compliance

Last year I wrote an article for EEWorld Online, comparing Channel Operating Margin (COM) with traditional Eye/BER analysis. This year, I’d like to delve into that topic a bit more with a technical blog series devoted to SerDes design. This is part one.

Every industry specification related to a SerDes protocol contains a set of standards that an interface is required to meet. A conformance, compliance, or validation testing is a suite of tests and measurements that the interface must comply with. The requirements to test a design for compliance are typically defined by the industry committee that supervised the development of the standard and can be included either in the body of the standard or provided as collaterals to the main specification.

A compliant device under test (DUT) must meet all the mechanical and electrical requirements of the particular specification. Testing and characterizing a design or DUT for compliance involves electronic test and measurement equipment such as oscilloscopes, signal generators, bit error rate testers (BERT), vector network analyzers (VNA), time-domain reflectometers (TDR), etc. Often, dedicated test fixtures are needed for performing those measurements. Compliance testing can be exhaustive, time-consuming, and expensive. Moreover, only a limited number of samples can be tested in the lab and those tests can be performed only at a late step in the process, after the first prototypes were assembled.

Simulations are not a replacement for measurements. In other words, compliance cannot be claimed based on simulated results. However, simulations can help reduce the number of design iterations required for a product to meet a particular specification’s requirements, thus shortening the development cycle and considerably reducing associated costs. Although the concept of virtual compliance is not new, it has not been fully and widely embraced by hardware designers thus far, mostly due to complexities associated with device modeling. In addition to that, performing compliance measurements and/or simulations requires a deep understanding and knowledge of the standards.

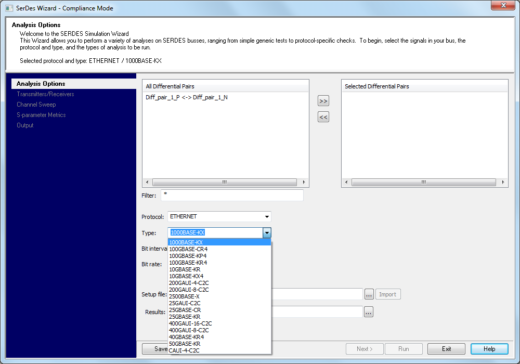

The HyperLynx® VX.2.3 release solves both of the above mentioned shortcomings with a new SerDes set of wizards especially designed to make the virtual-compliance process painless. Input to the wizards can be either extracted s-parameters, pre-layout LineSim® schematics or routed PCBs in BoardSim® format. If S-parameters are being used, they can come from a large variety of sources including measurements, HyperLynx, or third-party simulation tools.

The wizards’ compliance mode does not require external models as the transmitters and receiver devices are modelled using behavioral reference models based on the requirements of the specific standard used for simulations. Data rate, Tx voltage swing, signal edge rate, jitter, and feed forward equalizer (FFE) characteristics are all included in the Tx model. The effects of the continuous-time linear equalizer (CTLE) and decision feedback equalizer (DFE) are accounted for in the Rx model. The Tx and Rx packages are incorporated in the form of either Pi networks or S-parameters in touchstone format. Finally the transmitter and receiver terminations are added into the die-to-die channel characterization.

Channel compliance is performed according to the methods defined in each of the supported standards and can be eye diagrams, frequency domain metrics, and/or channel operating margin (COM). For more details about various channel compliance methods, please check out this SemiWiki.com article.

All the required compliance measurements and associated limits are built into the HyperLynx SerDes wizards, thus removing the burden of knowing all the specification details.

In conclusion, the SerDes wizards available in the HyperLynx VX2.3 release are an easy-to-use and efficient way to design compliant products without the need for specialized knowledge.