Inside Microsoft’s Journey to Transform IP QA with Solido IP Validation Suite

Picture a world-renowned band stepping on stage for a highly anticipated concert. The lights dim, the crowd roars, and then—chaos. The drummer launches into one song, the guitarist strums another, and the bassist is still tuning. What was supposed to be a masterpiece now sounds like a disaster.

This is exactly what happens when inconsistencies creep into a System-on-Chip (SoC) due to mismatched formats within an IP. Each format—whether Verilog, LEF, DEF, GDS, Liberty, CDL, or others—plays a crucial role. When these formats fail to align, the result isn’t a high-performing chip—it’s a debugging nightmare.

IP blocks are crucial for Next-Generation chip design

As modern SoCs become larger and more complex, design IPs have become essential building blocks. These IPs enable modularization and reuse of design components, making them critical for managing the increasing scale of chip designs. However, an IP is only as good as the synchronization of its internal formats. If the Verilog logic representation doesn’t match the DEF physical design, or the LEF abstraction is inconsistent with the GDS layout, it creates issues that disrupt the entire system.

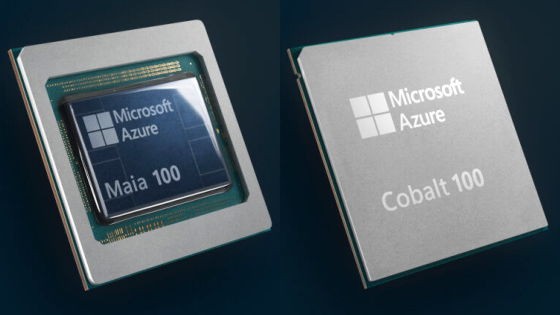

Ensuring consistency in Microsoft’s AI and HPC chips

Nowhere is IP format consistency more critical than in AI and high-performance computing (HPC) chips, such as Microsoft’s Maia and Cobalt processors. A discrepancy between formats could lead to misaligned layouts, connectivity issues, or incorrect power and timing analysis—causing inefficiencies that degrade performance. Just like a band that needs every musician in sync, an IP needs all its formats to be perfectly aligned to ensure the final silicon performs as expected.

A robust IP QA framework ensures consistency across different views, catching misalignments before they manifest as expensive silicon failures. By validating that all relevant formats—whether Verilog, LEF, DEF, GDS, Liberty, or others—are synchronized, the framework acts as a fine-tuning mechanism, ensuring optimal chip performance.

Join our Masterclass with Microsoft– Register Now!

On February 20, 2025, join us for our exclusive Masterclass session on Microsoft’s focus on IP QA using the Solido IP Validation Suite. We will explore Microsoft’s challenges and risks in IP QA and discuss how the Solido IP Validation Suite helps identify potential issues early in the design flow, ensuring superior-quality IP that operates in perfect harmony while accelerating time to market.

Because in the world of chip design, just like in music, harmony is everything.

Secure your spot now by registering here!