‘SPICE up’ your Verification this holiday season!

Just as I wrapped up my fancy Thanksgiving cooking marathon, I couldn’t help but draw parallels between the meticulous artistry of holiday cuisine and the intricacies of chip design. Coming from an Indian ethnic background, where spices are the soul of our cuisines, it dawned on me that in the realm of chip design, analog SPICE (Simulation Program with Integrated Circuit Emphasis) plays a similar pivotal role. In advanced chip design at lower tech nodes, it’s crucial to include sensitive analog blocks in transistor-level abstraction for accurate functional and timing verification. The less sensitive logic blocks can remain at higher abstraction. This mix of analog (SPICE) and digital (RTL/Verilog) abstraction ensures a thorough verification of their interaction in real world scenarios.

These mixed signal designs are essential components for many applications, such as data converters, digital radio, wireless communication, sensing, and automotive. However, designing and verifying mixed-signal ICs is not an easy task. It requires a combination of analog and digital expertise, advanced EDA tools, and efficient verification methodologies.

One of the main challenges of mixed-signal verification is the interaction between the analog and digital domains. Traditional verification solutions assume that analog and digital portions of the design can be verified separately, but this approach is inadequate for today’s complex and highly integrated mixed-signal ICs. Moreover, mixed-signal verification needs to consider various aspects, such as performance, functionality, power, noise, reliability, and testability.

Another challenge of mixed-signal verification is the speed and scalability. Today’s ICs are essentially large system on a chip (SoC), made of large and diverse subsystems that necessitate comprehensive verification coverage. Faster mixed-signal verification performance is absolutely essential to meet the tight time-to-market deadlines and quality standards. Additionally, mixed-signal verification needs to support different levels of hierarchy, from block-level to top-level, and different types of models, from transistor-level to behavioral-level.

A third challenge of mixed-signal verification is the usability and debuggability. Mixed-signal verification involves a team with diverse technical backgrounds and skill sets, such as analog block designers, digital block designers, modeling engineers, and system integrators. This team demands a verification solution with a simple and intuitive use model, and a seamless integration with the existing digital design verification infrastructure. Furthermore, mixed-signal verification requires effective debug tools and techniques, especially for finding and fixing errors at the interfaces between analog and digital blocks.

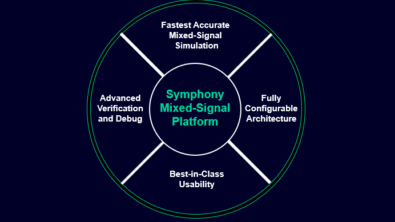

To address these challenges, Siemens’ Symphony platform offers a comprehensive and innovative mixed-signal verification solution that enables faster, easier, and more accurate verification of mixed-signal ICs.

Join us for a masterclass where we explore the intricacies of mixed-signal designs and reveal how Siemens’ Symphony is crafted to address your mixed signal verification challenges. Regardless of your level of expertise, whether you are a seasoned engineer or new to the field of mixed-signal verification, this masterclass offers an in-depth exploration of the Symphony platform. You will gain insights into its seamless plug-and-play capabilities for integration with industry-standard design environments, as well as advanced debugging features aimed at improving the verification turnaround time.

Upon completing this masterclass, you will be ready to “SPICE up your verification” this holiday season. 😊