How IROC Technologies leveraged a new place-and-route tool to tape out an aerospace SoC in three months

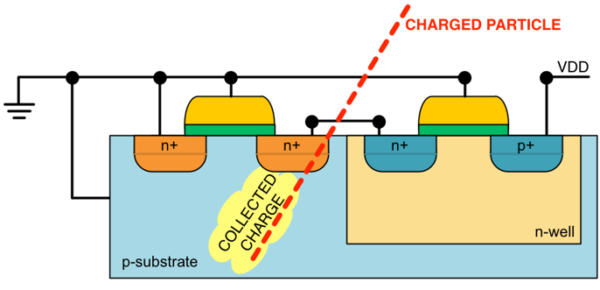

In space, having precise, reliable equipment is essential and when experts can’t be precise, they need to know the possible outcomes to minimize risk. In this customer story, the European Space Agency (ESA) tasked IROC Technologies to assess the suitability of Ultra Deep Submicron (UDSM) technology nodes below 22 nm for space applications. IROC set out to build an integrated circuit (IC) to act as the test vehicle for accurately measuring the effect of single events or soft errors on those devices due to radiation. They needed easy-to-use design software to develop the IC test vehicle under complex conditions and within a short timeframe.

Creating a Chip to Evaluate IC Tech for Aerospace Applications

Soft errors are not permanent faults but transient events that cause unexpected and complex behaviors that can affect the data integrity of the system and lead to mission failure. Before sending electronics into space, ESA needed to understand exactly how they will perform so they can manage expected outcomes. Each piece of technology needs to be managed at every stage of the design flow, from the circuit level to the ASIC, the board, and the system.

IROC’s challenge was to build an IC to act as the test vehicle for accurately measuring the reliability of various technologies (such as standard cells, memories, and IP) when exposed to radiation. And, they had three months to finish the chip.

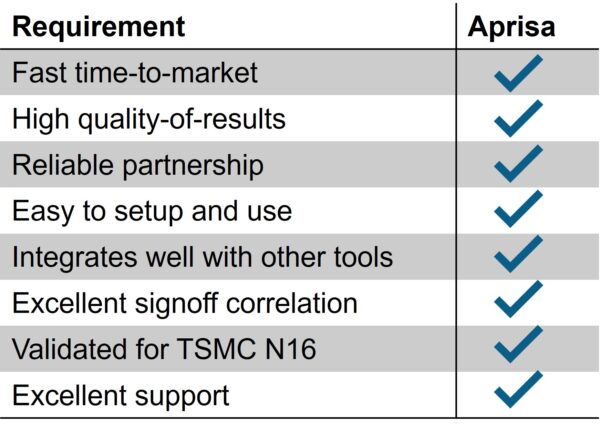

IROC’s Requirements for a Digital IC Design Flow

IROC is experienced in all phases of IC and system development but do not maintain a full-time group dedicated to IC design. To finish the chip on time, they needed an advanced node digital design flow that was easy to set up, easy to use, offered support and a fast time-to-tapeout. They also needed to minimize the risks that could delay tapeout when selecting an IC design vendor, ensuring TSMC N16 process validation, compatibility with other tools (including 3rd party), and the benefit of ease of use, easy to setup and to adopt.

After reaching out to a Siemens’ Aprisa application engineer, IROC and Aprisa teams worked together to determine the software and support required for the project. Because IROC was designing a new IC from scratch with a new design flow, new software, and on a very tight schedule, selecting Aprisa helped reduce risks so the IROC team could focus on meeting the tapeout schedule.

“Aprisa offered great integration and support. That was a bright spot in this very challenging project.”

Maximilien Glorieux CTO, IROC Technologies

Getting Started with Aprisa for Place-and-Route

The IROC designers completed the first pass of placement within a few days of setting up the software. The team started with a small block, got quite good results, and then implemented larger blocks. The Aprisa software can read TSMC technology files directly, perform complicated design partitioning and meet strict hold time constraints with its near signoff quality timing analysis engine.

As expected, all the software in the design flow operated together smoothly. The Aprisa software architecture is flexible and uses all open industry standards, so interoperability with other IC design software, whether from Siemens or a third party, wasn’t an issue. Aprisa is certified on TSMC technology down to N6, as well as leading process nodes for other major foundries and is in the process of gaining certification for 5nm and 4nm nodes.

Results Exceeded Expectations

IROC built a new digital design flow, installed and set up the tools, completed the design and reached tapeout in three months. The design was manufactured and underwent a battery of analyses to generate reliability data for ESA. Aprisa was key to IROC’s success because they were able to implement a powerful and flexible physical implementation flow that was easy to use, fast, technology-ready, and with excellent correlation with sign-off which greatly reduced iterations.

The Aprisa software is detail-route-centric physical design software for the modern SoC. Designers get excellent quality-of-results and fast runtimes. Aprisa helps designers minimize iterations, improve performance/power/area trade-offs and reduce time-to-closure by pulling detail-route visibility earlier in the flow.