Let AI help with macro placement during place and route

Aprisa’s AI-driven Auto Macro Placement (AMP) creates a high-quality floorplan in a fraction of the time needed for manual macro placement.

Is there a need for an automatic macro placer?

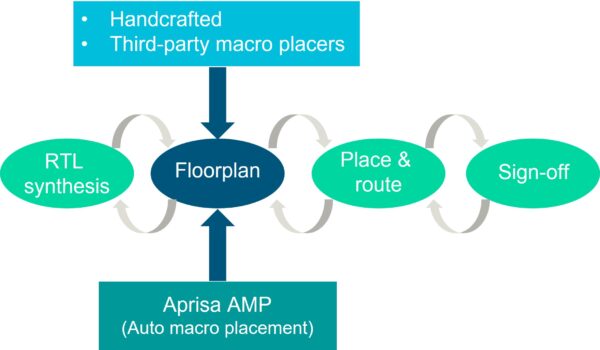

Floorplan quality, and especially macro placement, has increasingly become a critical challenge to achieving better physical design PPA (performance, power, area) and a faster total turnaround time. This is due to several factors (figure 1):

- The physical-aware RTL synthesis tools need to extract physical information based on macro placement and a rough standard cell placement, to provide accurate results that can carry to place and route.

- Downstream, the QoR (quality of results) achieved by the place and route flow is also largely sensitive to macro placement. A bad floorplan will lead to painful iterations and much longer total turnaround time.

Figure 1. The RTL-to-GDSII flow showing options available to complete the floorplanning step and its relationship to the entire flow.

Traditionally, floorplan and macro placement are handcrafted by a few experts based on design experience, project knowledge from previous versions, and intuition. This method used to work fine for chips with dozens of macros. However, since modern SoC designs contain hundreds of macros, there is a need for at least a semi-automatic way to place these macros.

Most macro placers on the market today provide some guidance to get designers started with their floorplan but fall short of a full solution and end up limiting PPA gains. There are even a couple of AI packages for macro placement that attempt to improve this very tedious task but cannot yet provide the QoR that designers need to achieve.

Aprisa’s AI-driven AMP offers a unique advantage, leading to a floorplan in a short amount of time (as short as an hour) compared to any floorplan generated in a traditional manner, which takes weeks or months. The fast runtime is great, but the main benefit is the high quality of the floorplan that mimics how designers would naturally align the blocks. In addition, Aprisa’s AMP keeps track of timing and congestion, pulling macros that can cause issues down the flow to a more optimal location.

These qualities make automating floorplanning a key improvement for designers during their RTL-to-GDSII cycles. Aprisa minimizes the dedicated effort by design experts to place macros, reducing the many iterations to make adjustments based on congestion and timing, and slashes the overall time spent during this step in the flow.

Key advantages of Aprisa’s AI-driven AMP

Aprisa’s patent-pending AMP offers fully automatic features with unique advantages:

- The macro global placement feature relies on Aprisa’s competitive timing-driven engine to naturally place the macros that belong to the same hierarchical module closer together

- Macros with the same physical dimension are grouped together to ensure proper alignment and better routability

- AMP automatically avoids macro placement that results in unusable space on the chip, ensuring efficient core utilization

- Aprisa contains built-in AI-based design algorithms to legalize the macro placement and avoid common floorplanning issues, such as bottlenecks created by narrow channels

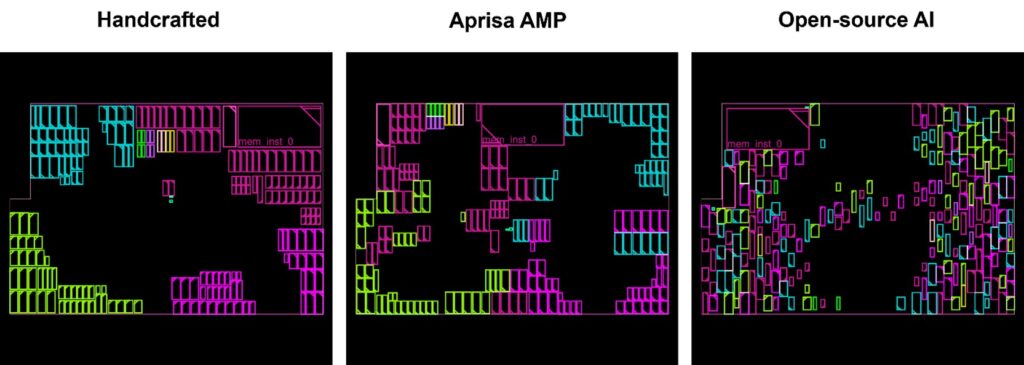

Figure 2 shows an example of how Aprisa’s AMP naturally puts macros that belong to the same hierarchical module (modules are noted by a unique color), in close physical proximity to each other, and most macros are properly aligned. For this testcase, Aprisa’s AMP floorplan achieved 10% shorter wirelength and 15% less leakage power, versus the handcrafted floorplan after full flow final QoR results. Timing closure is achieved for both Aprisa’s AMP floorplan and handcrafted floorplan. In terms of runtime, it took around 1 hour for Aprisa’s AMP to generate the floorplan for this design compared to weeks for the handcrafted floorplan.

Figure 2 Floorplanning comparisons between handcrafted vs. Aprisa AMP vs. open-source AI package, for a sample design.

An open-source AI package was also evaluated on this design to place the macros. Although the tool also ran fast, it mixed up the macros belonging to different hierarchical modules as it does not seem to have a native alignment mechanism. As a result, the open-source package floorplan had 30% longer wirelength than Aprisa’s AMP floorplan, and using the open-source floorplan, the P&R flow could not close timing for this design.

Aprisa’s AI-driven AMP benefits not only from the initial algorithms that mimics the handcrafted floorplanning methodologies but also from Aprisa’s competitive timing engine, to produce a floorplan with desirable QoR results.

Aprisa’s AMP offers other useful semi-automatic features to improve the final QoR and help the designers find the most optimal macro placement for their specific ICs. These features can be run on top of an AMP generated floorplan, but also allow designers to input their expertise, especially on complex designs where they may have spent several versions fine-tuning to improve their final PPA.

A few of the available semi-automatic features include:

- Perform manual repack on selected macros to fix the remaining bottleneck

- Tune some parameters to explore best possible floorplan

- Choose to manually fix selected large macros on the chip boundary, and let the timing-driven engine find the best location for the smaller macros in the middle of the chip

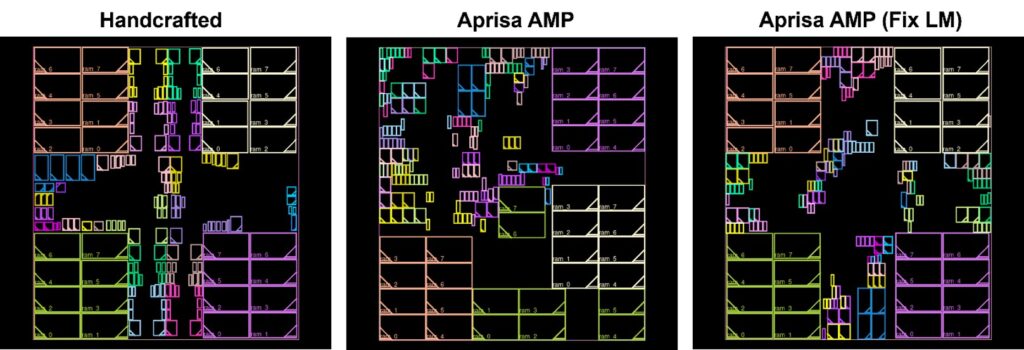

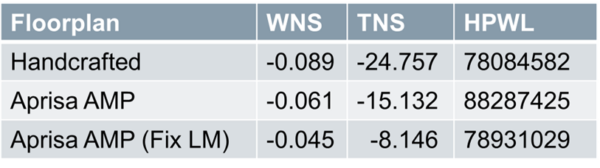

The examples shown in figure 3 illustrate how Aprisa’s semi-automatic large macro fixing achieved additional improvement on timing just by finding the most optimal macro placement at the floorplan stage.

Figure 3. Comparison between handcrafted floorplan vs. AMP base vs. AMP after pre-fixing large macros.

In the example on Figure 3, Aprisa’s AMP placed large macros towards the lower left corner of the design area. Even though this floorplan achieved better timing than the handcrafted floorplan, it has 13% longer wirelength. By fixing the large macros at the boundary of the design area, Aprisa AMP was able to optimize the location of smaller macros in the center the design area. This improvement achieved even better timing, and similar wirelength as the handcrafted floorplan.

Conclusion

Aprisa’s AMP can generate a high-quality floorplan with its fully automatic flow for complex designs with hundreds of macros. This is possible because the AMP technology is based on Siemens’ highly competitive Aprisa timing engine and built-in AI-based design algorithms and alignment techniques. Its additional flexible semi-automatic features further improve the final QoR and gives designers the opportunity to reduce their floorplan iterations and effort from weeks or months to only a few hours. It also means that design experts can focus on other aspects of their project metric tradeoffs and requirements.

With Aprisa’s tight pre-route to post-route correlation and AMP technology, designers can confidently determine their PPA metrics as early in the flow as the placement stage. Instead of running a myriad of iterations to find the best possible floorplan, they can utilize some of the saved time to figure out what tradeoff metrics can give them the optimal PPA and TAT for their projects.

Aprisa’s AMP is yet another feature that enhances the out-of-the-box methodologies and ease of use that designers have come to expect from Aprisa, alleviating the time designers need to spend on crafting the most optimal floorplan for the best QoR.