Aim for power first for better PPA in place-and-route

Among the key metrics in IC place-and-route—performance, power, and area (PPA) — performance has traditionally been the primary focus. Low power has been gaining in importance though, particularly at today’s advanced process nodes. Of course, no one wants lower-performing chips, so place-and-route tools employ a variety of strategies to achieve the lowest power without sacrificing performance.

Achieving low-power during place-and-route depends on two key factors:

- How well the software handles multiple power domains

- The kind of optimizations the software performs throughout the flow

The place-and-route software from Siemens, Aprisa, helps designers address the many challenges of low-power designs. Aprisa is the most flexible IC place-and-route tool on the market—it accepts all industry-standard power formats, has excellent correlation to third-party signoff tools, and is easy to install, set up, and use. With effective technology and impressive usability, the Aprisa software ensures cost-effective tape-outs for power-sensitive designs. You can learn more about the Aprisa low-power solutions in our new technical paper.

Managing multiple power domains

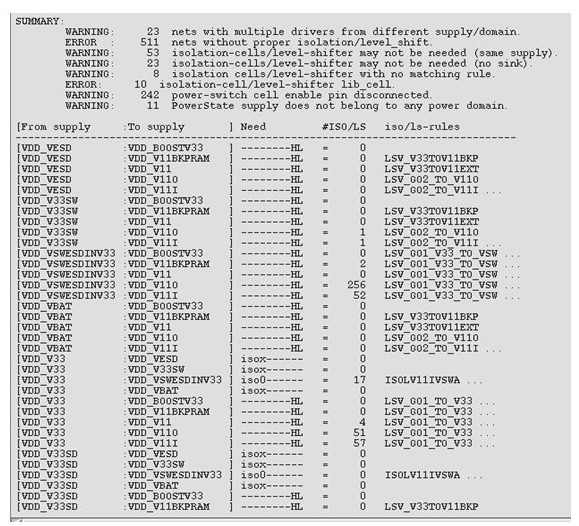

Multi-power domain support ensures all the elements required in a low power design are included and used in accordance with the low-power specs. The software used in the digital implementation flow must be able to buffer on multiple power domains without errors and perform placement of all power management cells such as level shifters, isolation cells, power switch cells, and retention flip-flops. Power-sensitive designs also require routing secondary power/ground pins and routing to the power grid inside the voltage islands.

Aprisa has comprehensive multi-power domain support, and it supports the United Power Format (UPF). Aprisa can automatically insert power management cells, such as isolation cells, level shifters, power switches, always-on/regular buffer selection. Its unique Power Domain Checker can flag the errors related to power domain, cell placement, connectivity, and buffering.

Optimizing designs for low power

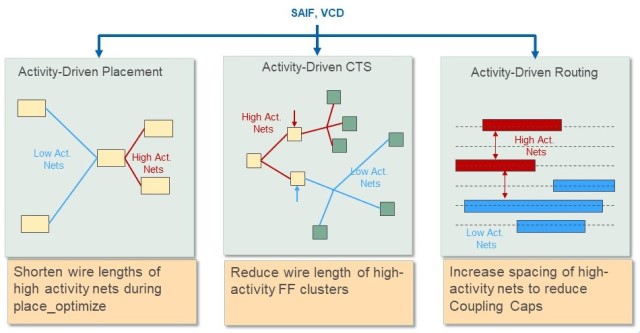

With the design goal of meeting strict power specifications without sacrificing performance, the Aprisa PowerFirst methodology takes “best power” as the top priority and works towards that goal throughout the flow, using activity-based placement and routing for lower dynamic power. By starting with the power metric as the top goal during optimization, the place-and-route flow can achieve the best possible power for that node, library, and design specs, and then optimize from that point to reach the timing target. This method is more effective than trying to recover power once the most power-hungry cells have already been used in the design to achieve timing.

Techniques deployed in the PowerFirst methodology include:

- Clock transition fixing for better power

- Tradeoff small timing for large power reduction in CTS

- Multi-bit-register merging and de-merging

- Full LVF analysis and optimization to reduce over-design

Example Results from PowerFirst Methodology

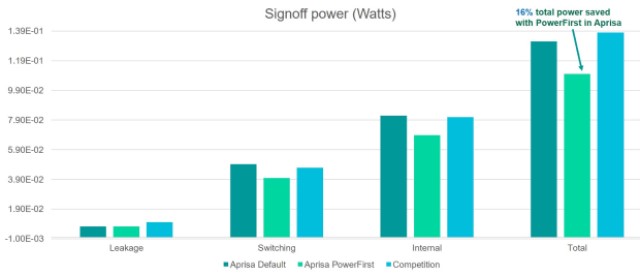

PowerFirst optimization reduces the internal, switching, and leakage power of the most power-sensitive designs while minimizing timing tradeoffs. In an industrial design, a DDR PHY in 7 nm with about 1.3M instances and a 1 GHz frequency, PowerFirst techniques reduce the total power by 16% compared to Aprisa in timing-only mode while maintaining the achieved timing correlated to signoff. Aprisa’s results also beat the incumbent place-and-route solution.

Built-in Power Domain Checker

Aprisa offers a comprehensive power domain checker within the tool that checks multi-voltage setup, power management cells, and correct connectivity. It can identify all the power domain-related errors without the need of an external verification tool and long before going to signoff, which can ensure correct-by-design low-power methodology and use of power management cells as required.

About Aprisa

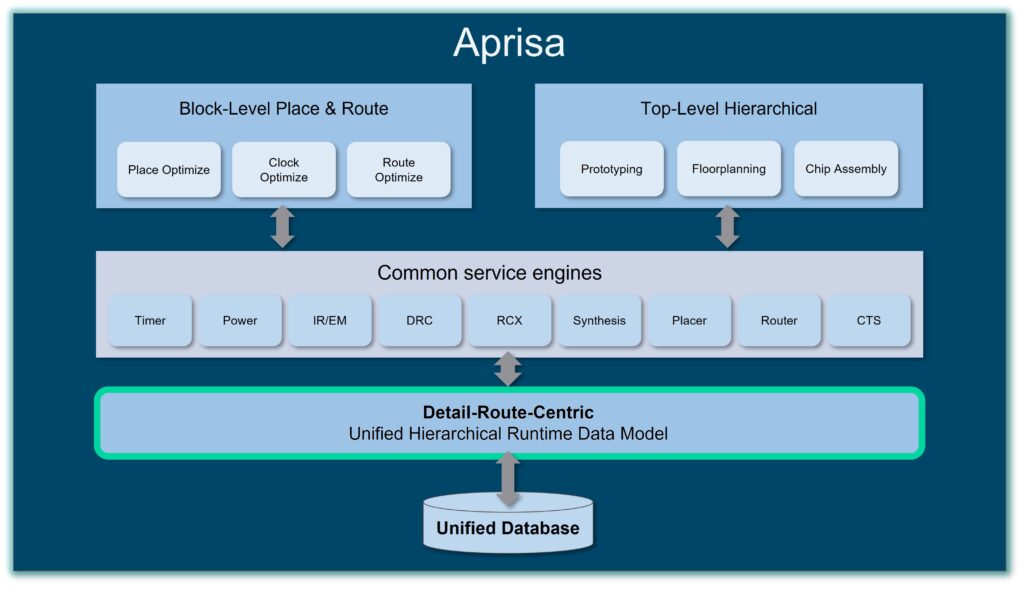

The Siemens team has put a lot of thought, ingenuity, and investment into making Aprisa easy to use, easy to adopt, fast, and capable of producing the best PPA for today’s hierarchical and block-level designs. The detail-route-centric Aprisa software was built from the ground up using modern algorithms.

Aprisa uses a unified data model that is shared throughout the entire flow, so there are no data or format conversions between implementation steps. In addition, the unified data model allows real routing information and parasitics to be available to each step in the flow, resulting in consistent timing and DRC and excellent correlation to signoff tools.

Download the technical paper to learn more about using Aprisa for low-power SoCs.