The “Why” and “Where” of Serial Channel Design

Author: Mark Brown, Senior Instructional Designer and Technical Trainer, Siemens EDA Learning Services

Have you ever wondered why you are having an issue with the performance of the serial channel you are designing? Or, if you do know why, do you know where the problem exists?

The new HyperLynx Serial Channel Design class is essential for anyone who is using HyperLynx during the design process of Serial channels. This class not only discusses the many facets which need to be considered while using HyperLynx to design your serial channels, but also helps you understand the resources at your disposal to answer the questions of “Why am I having an issue with my channel?” and “Where is the problem in my interconnect?”.

You will not only run the tools, but also explore the information in the reports. Understanding the information in the reports provides the kind of actionable results you can apply directly to the design. For example, the TDR plots provide the location and magnitude of impedance discontinuities allowing you to optimize that region. In the class you will explore a design using sweeping techniques for both the 2D and 3D PCB structures.

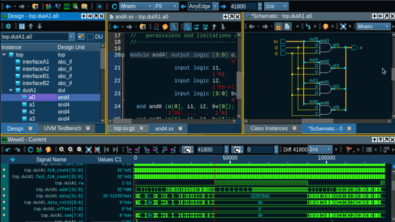

The class covers the HyperLynx tools which can be used to analyze and optimize your SerDes interfaces. These include LineSim, BoardSim, the Full-Wave Solver, and the 3D Explorer. In LineSim, for example, you will go through the process of sweeping physical parameters of a 3D structure using HyperLynx 3D Explorer, creating the 3D models using the Full-wave solver, and evaluating the performance for constraint generation.

In BoardSim, you will use an automated 3D region extraction process to identify the regions which need to be modeled in 3D and create the physical 3D structures, then create the 3D models, and evaluate the performance. Structures which perform poorly, can be loaded into the Full-wave solver, modified, and performance verified before making changes to the actual layout.

These activities will save time, money, and effort in ensuring the performance of the channels you design will meet or exceed your customer’s expectations.

The class is written to address the concerns of both the integrated Xpedition PCB design flow and non-Xpedition flows. For those using the integrated Xpedition PCB design flow, the class has a summary of the entire process from schematic to HyperLynx so you have a full appreciation of the inter-dependencies among the tools.

For more details on the course content, visit here.