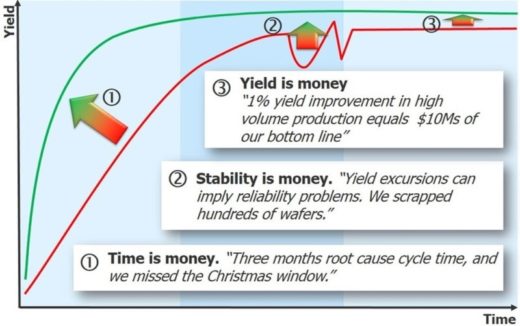

Yield is Money

By Matt Knowles – Mentor, A Siemens Business

Have yield issues delayed your product introduction or sales? Would a 1% improvement in yield have a significant impact on your bottom line? Do you see different yields for different products on comparable processes?

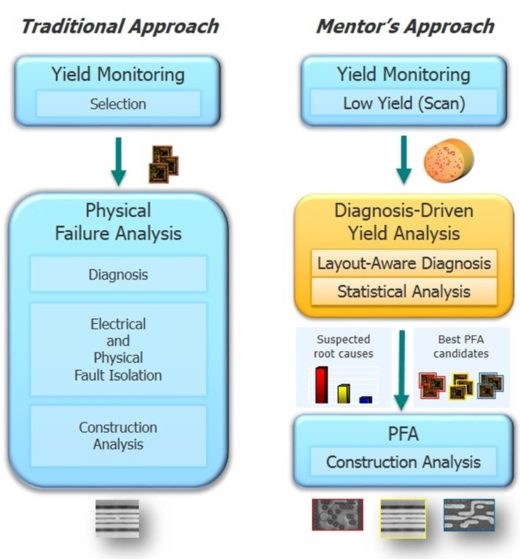

If you answered “yes” to any of these questions, you know that yield=money and whether you are trying to accelerate yield ramp on a new process or boost your margins on established nodes, you need a way to find and fix yield limiters. Diagnosis-driven yield analysis, DDYA, is a methodology for digital semiconductor devices that leverages production test results, volume scan diagnosis, and statistical analysis to identify the cause of yield loss prior to failure analysis. This methodology can reduce the time to root cause by 75-90%, and identify systematic yield limiters that would otherwise never be found.

Scan diagnosis leverages a design description, scan test patterns, and fail data from a tester to identify “suspects”, i.e. the most likely defects that caused the failures during digital test. Once upon a time, scan diagnosis alone could be used to find the likely physical location of defects.

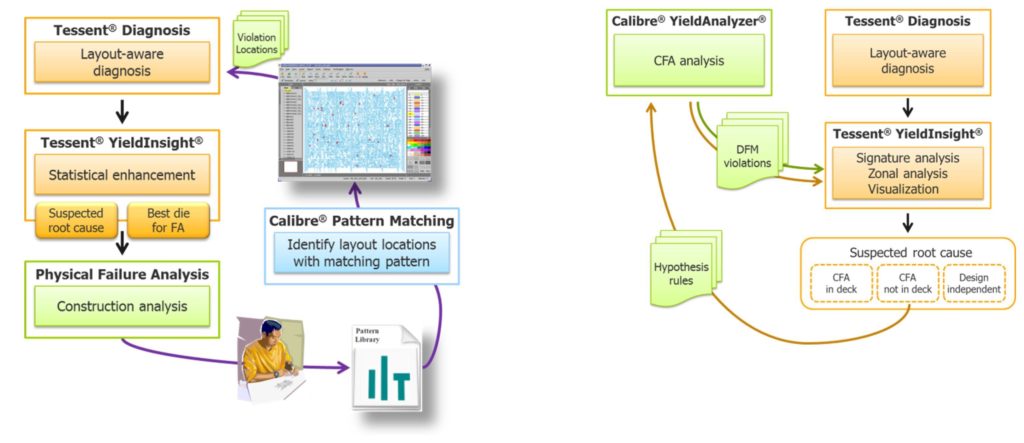

DDYA represents a different approach. Rather than just using diagnosis for defect localization, diagnosis is used to determine the underlying root causes and the best physical failure analysis (PFA) candidates in a batch such as a wafer or lot of failing devices. This is an improvement in many ways, including improving PFA success, reducing PFA time, finding the root cause much faster, and finding previously hidden yield limiters.

To make DDYA a reality, there are two key components that need to be in place:

Diagnosis needs to produce the type of data that is meaningful for yield learning – this involves leveraging layout information like cell type, via type, layer, and critical area. Plus, because as much as 50% of defects can be internal to the cells, a transistor-level (Cell-Aware) diagnosis using fault models derived from analog simulation is very beneficial, as is advanced scan chain diagnosis and at-speed diagnosis. You also need a lot of data to effectively leverage diagnosis for yield analysis, so diagnosis must be run on production test patterns, in presence of scan test compression, and with minimum impact on test time.

A DFM-aware yield analysis helps resolve systematic defects that are design-process related, but there are some challenges to consider. For example, when you find a defect location that correlates with a DFM violation, how to you know that the violation is the actual cause of the defect? And what if a defect is caused by a design feature that isn’t modeled by the existing DFM rules?

To deal with these situations, we correlate layout-aware diagnosis data with Critical Feature Analysis (CFA) results from Calibre® YieldAnalyzer®. If a suspect defect is partially or fully in the same layer and location as a DFM rule violation, this suspect is said to correlate with that DFM rule.

The analysis of diagnosis results must take the ambiguity of diagnosis results into consideration – this means separating the valuable information from the noise. We use two key techniques: Zonal analysis, which analyzes the distribution of a defect signature to help spot patterns that point to systematic issues; and root cause deconvolution (RCD), a statistical enhancement technology that increases the PFA success rate and dramatically reduces the PFA cycle time from months to days. Where layout-aware diagnosis points to a segment, RCD can isolate a particular root cause in that segment.

For more details and to see examples of using Tessent to find systematic yield problems, select devices for failure analysis, and identify DFM-related yield loss, see the whitepaper Overcoming Systematic Yield Limiters with Diagnosis-Driven Yield Analysis

An effective diagnosis-driven yield analysis flow can reduce the cycle time to root cause of yield loss by 75-90%. This translates into faster yield ramp for new processes and improved profit from mature processes.