Trends in DFT…according to you

A look at the top downloaded Tessent whitepapers reveals DFT challenges

To make the software that DFT, test, and product engineers rely on, the Tessent team stays deeply involved in both research and development. Through partnerships, customer engagements, and academic outreach, it’s fair to say the test genius at Mentor know what’s going on.

However, we can also detect trends based on the interest in whitepapers published on mentor.com. While this list comes as no surprise, it does offer the opportunity to go back and read up on topics you may have missed, but many of your peers did not. The top downloaded whitepapers are:

1. AI Chip DFT Techniques for Aggressive Time-to-Market

AI chips have aggressive time-to-market goals. Designers can shave significant time off of DFT and silicon bring up using the techniques described in this paper. Leading AI semiconductor companies have already had success with Tessent DFT tools.

2. ON Semiconductor Reduces Memory BIST Insertion Time by 6X with Tessent Hierarchical Flow

This paper describes a case study on the insertion of memory BIST for an ON Semiconductor multi-million gate-level netlist with 300 memory instances. The physical implementation will be done using a flat layout. Two different methodologies can be applied when it comes to physical implementation; hierarchical or fullflat. When performing physical implementation as full-flat flow, typically the DFT methodology also follows the same decision. Thus, DFT is to be inserted once for the entire gate-level design.

3. Tessent Hierarchical ATPG Reference Flow for Arm Cortex A75

Arm and Mentor have jointly developed a reference flow for a hierarchical DFT and ATPG implementation with Tessent® for any Arm subsystem based on Cortex A-series IP. The reference flow, described in this paper, provides documentation, seamless interfaces, and scripts that accelerate the implementation of a hierarchical test solution. Arm and Mentor are dedicated to enabling customer success, regardless of their level of experience implementing hierarchical ATPG on Arm cores.

4. Simplifying silicon bring-up and debug on ATE equipment with ATE-Connect

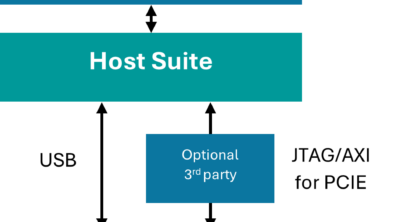

The silicon bring-up process is ripe for improvement. Tessent SiliconInsight with ATE-Connect technology eliminates communication barriers between proprietary tester-specific software and DFT platforms, which accelerates debug of IJTAG devices, speeds product ramps, and reduces time-to-market for products in 5G wireless communications, autonomous driving, and artificial intelligence.

5. Improve Volume Scan Diagnosis Throughput 10X with Dynamic Partitioning

Performing volume scan diagnosis on today’s large, advanced node designs puts demands on turn-around-time and compute resources. This paper describes a new technique to maximize diagnosis throughput while performing ever more demanding scan diagnosis. The dynamic partitioning technology in Tessent Diagnosis enables in a 50% reduction in scan diagnosis time using only 20% of the typical memory. This new dynamic partitioning technology makes a larger volume of scan diagnosis results available much faster, increasing the overall throughput of failure diagnosis by 10X.

The DFT challenges facing real designs today are rooted in several factors: new chip architectures, new process technologies, and more pressure on design schedule and cost. The Tessent solutions described in these papers are designed to help maximize the efficiency of DFT, test, and diagnosis flows of today and tomorrow.