How-to implement hierarchical DFT on Arm cores

The new reference flow jointly developed by Arm and Mentor for hierarchical DFT and ATPG with Tessent is described in depth by Mentor’s technical marketing engineer Sean Shen in an informational video that DFT engineers may want to watch…

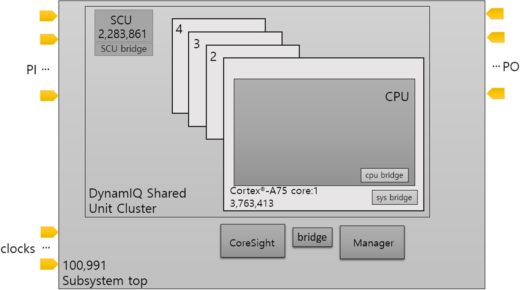

Mentor and Arm have maintained a long-term partnership to improve testing of Arm cores. Arm and Mentor know that our customers are integrating hundreds of IP subsystems on their SoCs, including processors like the Arm Cortex®-A75 (Figure 1), and would benefit from a reference flow. Success for designers is easier when their EDA and IP vendors cooperate, which is why Mentor and Arm have continued their closer partnership in developing reference flows for so many years.

This latest reference flow reflects the fact that large, complex, multi-core SoCs need better and more efficient strategies for DFT and ATPG. The adoption of hierarchical DFT has been growing quickly, as it proves it’s value for large, complex designs. With hierarchical DFT, all the DFT is completed at the block level and then replicated to the top level. Hierarchical DFT moves the DFT efforts early in the design flow and reduces ATPG runtime and compute resources by 10x.

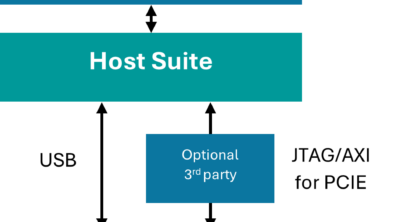

The video demonstrates the RTL-based hierarchical DFT flow and points to further resources available for designers working with Arm Cortex cores.

This DFT flow provides a simple and verified hierarchical test methodology for cost-effective, high-quality test of Arm IP, making it easier to reap the benefits of hierarchical DFT. The flow defines all the steps necessary to implement RTL-level hierarchical DFT, including scripts, interfaces, and documentation.

Watch the video from technical marketing engineer Sean Shen here.