Control test cost with low pin count test

By Rahul Singhal – Mentor, A Siemens Business

Several design trends, including increased design sizes and the use of advanced fault models, have led to an exponential increase in test pattern count. More test patterns lead directly to longer test times and higher test costs.

An interesting side effect of growing design sizes is that the number of pins doesn’t increase at the same rate as the design size. The number of transistors sizes grow exponentially, but the number of pins grows linearly. The result is less available bandwidth for test pattern application.

So, to control the increase in test cost it helps to compress the test patterns and apply them in fewer cycles with fewer test pins. So how much compression do you need and how few pins can you get away with to get the balance of throughput, cost, time, and coverage?

ICs are increasingly being designed with very few test pins, so a low-pin interface for test is the only option. For many designs, using a good ATPG compression solution is enough, but there are special test controllers that can maintain high-quality test and control costs in extremely test pin limited designs.

Mentor’s Tessent TestKompress offers three LPCT controllers:

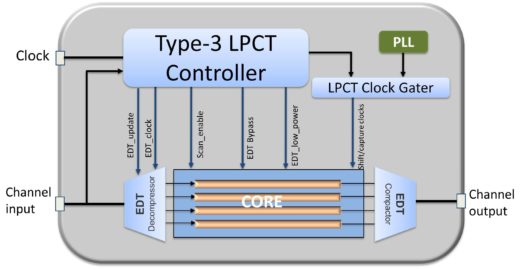

- Type 3—a three-pin LPCT controller for low power and extremely test pin limited applications such as image-sensing ICs. This LPCT controller has demonstrated high data and test time compression ratios of 65X with no impact to test coverage or test quality.

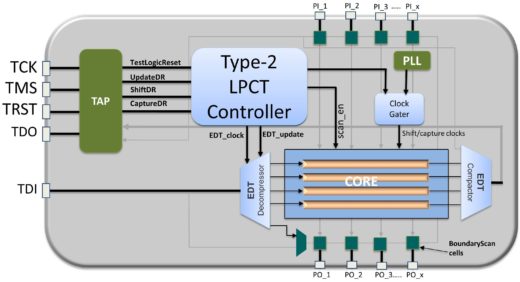

- Type 2—uses a TAP and modified boundary scan cells (reduced pin count testing cell) to provide access to functional pins to achieve higher test coverage of logic between scan cells and top-level pins.

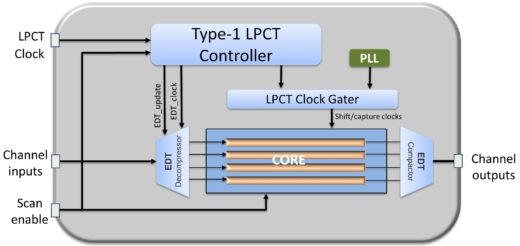

- Type 1— generates control signals internally for Tessent TestKompress effectively providing more pins for applying test data which reduces test data volume and test costs.

There are good reasons to use low pin count test, including benefits to top-level routing congestion, managing pin limitations, improving hierarchical ATPG, reducing ATE costs, improving wafer test, and performing multi-site testing. Tessent TestKompres LPCT is an effective solution for managing test costs.

For details on these LPCT controllers, download our new whitepaper Reduce Test Cost by Combining Low Pin Count Test and Scan Compression