Using Data Bus Inversion to Mitigate Simultaneously Switching Noise

This is the third post in a three part series that examines the problem of SSN and explores methods of reducing SSN in your designs. Click to read Part 1 and Part 2 of this 3 part blog series.

In the first installment of our blog series on Simultaneously Switching Noise, we went through an overview of SSN and explained its relevance to high-speed parallel busses such as DDR4. In the second post, we examined the effects of a poorly designed Power Distribution Network (PDN) on SSN and signal integrity. This final post will elaborate further on the Data Bus Inversion (DBI) option introduced at the conclusion of the previous post.

DBI is an optional feature in DDR4. If DBI is enabled, then when the driver (controller during a write or DRAM during a read) is sending out data on a lane, it counts the number of “0” (logic low) bits. If the number of bits driving “0” in the lane is five or more, then the entire byte is inverted, and a ninth bit indicating DBI is asserted low. This ensures that out of the 8 DQ bits and the 9th DBI bit, at least five bits are “1” during any given transaction. This also ensures that out of the entire data lane, the maximum total number of signals transitioning is either five 1’s to 9 1’s or vice-versa. There can never be a situation where all bits go from 0 to 1 or from 1 to 0.

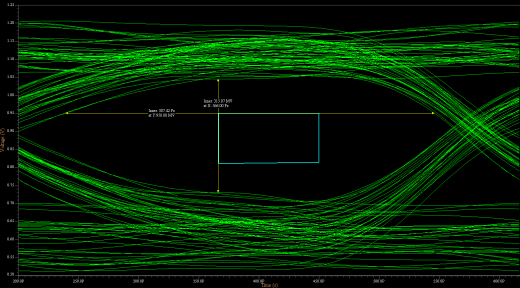

So, if we run the same data bus with data patterns which would be the output of the DBI logic, we get the waveform for DQ0 in Figure 1.

The eye-height for DQ0 in this case is over 315mV, which surpasses all the other conditions. Now, since DBI is data dependent, the benefits of DBI may vary and need to be analyzed before implementation.

Thank you for following our blog series on SSN—we hope you find this information valuable and share your thoughts in the comments. With a good design of the PDN, and possibly selecting the DBI feature in DDR4, SSN shouldn’t be a bother in your design. If you’d like to learn more about SSN and similar challenges, check out our white paper “DDR4 Board Design and Signal Integrity Challenges,” which was recently nominated for the DesignCon Best Paper Award.