Early Software Prototyping: Mitigating Risks Before Silicon

The Software Verification Challenge

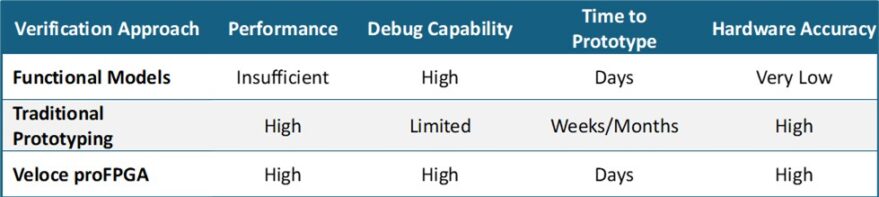

When developing complex systems-on-chip (SoC), software teams traditionally face an impossible choice: use slow functional models that cannot verify real-time behavior or wait months for traditional Field Programmable Gate Array (FPGA) prototypes with limited debug capabilities. By the time silicon arrives, it is often too late to address critical software issues without costly delays.

Breaking the Speed vs. Debug Tradeoff

Siemens Veloce proFPGA CS eliminates this dilemma by providing:

- Production-level performance for verifying real-time behavior

- Software-centric debug capabilities not found in traditional FPGA prototypes

- Rapid deployment measured in days rather than months

- Hardware-accurate behavior beyond what functional models can provide

Veloce proFPGA CS revolutionizes software debugging with two powerful capabilities not found in traditional prototypes. First, “probeless read” allows engineers to take snapshots of arbitrary registers without interrupting system operation, perfect for monitoring status registers during real time execution. Second, and more importantly, “full visibility readback” provides complete waveform visibility across the entire design without predefined probe points. This means software teams can analyze any signal in the system without the daylong recompilation cycles required by traditional prototypes. Veloce proFPGA CS maintains accurate simulation time even when design clocks are paused for debugging, transforming software verification from a slow, planned activity into an interactive, responsive process.

Real-world Impact

A leading automotive manufacturer using Veloce proFPGA CS identified critical timing issues in their advanced driver assistance systems three months before silicon availability. These issues would have remained hidden in simulation environments and could have delayed product launch by up to six months if discovered after silicon arrival.

Technical Differentiation

Looking Beyond First Silicon

Early software verification does not just solve immediate challenges; it transforms your entire development process. Teams can verify customer requirements earlier, accelerate integration, and enter the market with thoroughly tested solutions that have been operating at production speeds for months before silicon arrives. Click here for more information.