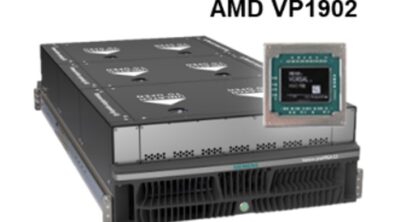

Veloce proFPGA CS Changes the Game for Software Prototyping

With the AMD VP1902 FPGA device boasting double the capacity, you unlock a whole new level of performance and cost-effectiveness.

Whether pushing the boundaries of SoC verification, validating complex IP blocks, or simulating massive software workloads, the Veloce proFPGA CS software prototyping platform, equipped with the VP1902 FPGA device, doubles the capacity and delivers verification success.

Performance. You can map more of your design onto a single chip. This means that fewer FPGA devices are needed overall, resulting in streamlined mapping and improved performance. The benefits extend beyond performance. With fewer FPGA devices required, the cost per gate for your prototyping platform plummets. That’s right – 50% lower cost per gate means significant savings for your budget. You can achieve more with less, maximizing the performance of your resources.

Consolidation: Mapping your design onto a single high-capacity FPGA simplifies the setup and configuration process. No more juggling multiple devices or dealing with complex interconnectivity.

Simplifying setup and configuration means faster and more efficient prototype bring-up, allowing you to accelerate your development cycle like never before. You have more opportunities to test different scenarios, catch potential corner case issues, and optimize the quality of your design.

To learn more, download the Veloce proFPGA CS factsheet or email Romain Petit romain.petit@siemens.com for details.

Gabriele Pulini is a Product Marketing Manager in the Hardware-assisted Verification Division at Siemens EDA. He has more than 20 years of EDA experience, with 14 years specializing in hardware hardware-assisted verification.