Article Roundup: Calibre nmLVS-Recon to streamline IC circuit verification, Design and verify 5G systems – Part 1, Running With O-RAN, AV Transformation Design and Verification Turbocharges OEMs, Mapping Neurons to a Model

- Calibre nmLVS-Recon to streamline IC circuit verification

- Design and verify 5G systems, part 1

- Running With O-RAN

- AV Transformation Design and Verification Turbocharges OEMs

- Mapping Neurons to a Model

- Calibre nmLVS-Recon to streamline IC circuit verification

ElectronicSpecifier.com

In this article, the author talks about Mentor’s extension of their Calibre Recon technology to the Calibre nmLVS circuit verification. The Calibre nmLVS-Recon solution helps speed overall circuit verification turnaround time by helping system-on-chip (SoC) engineers, circuit designers, and IC circuit verification teams identify and resolve selected systemic errors early in the development phase.

Design and verify 5G systems, part 1

EDN

In this article, the author highlights the important technical requirements for 5G communication. He further stressed that the 5G standard is a leap forward from all four previous wireless standards, promising faster speeds, higher data transfer rates, and lower latency with wider coverage and that 5G will put an end to congestion and latency issues hampering the aging 4G standard.

Running With O-RAN

SemiEngineering

O-RAN is a complex standard, with a six layer stack of functionality and there are currently 9 technical workgroups that are defining the specification. It is the architectural foundation for companies to build out intelligent 5G systems. 5G SoCs demand a new verification approach that meets the challenges of the exponential rise in required tests: a verification flow for pre- and post-silicon. In this article, the author highlights that open and flexible 5G standards are driving new development of highly customized hardware and by using O-RAN teams can bring their tested solutions to market faster.

AV Transformation Design and Verification Turbocharges OEMs

ElectronicDesign

In this article, the author explains in detail on how emulation delivers on the industry need for pre-silicon verification of AV chips. Closed-loop validation hinges on rigorous pre-silicon validation of deterministic (rules-based) and non-deterministic (AI-based) approaches to safe self-driving in the context of the full digital twin. Emulation provides a portfolio addressing design exploration, validation, and verification of autonomous vehicles to optimize R&D spending on AV development. The author further stresses that OEMs will be able to create a sustainable, competitive advantage in the market by embracing this transformational change.

Mapping Neurons to a Model

MentorBlogs

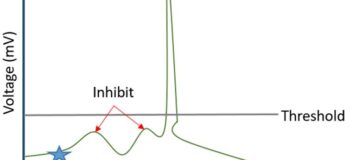

This blog explores mapping the neuron of the brain into a software model. A neuron receives inputs that constantly add (excite) and subtract (inhibit) based on what the brain is thinking about. When the total input reaches a threshold voltage, where the excitation outweighs the inhibition, an electrical spike occurs, triggering a synaptic release which allows communication to another set of neurons. Developing a model that can be used for an AI application, like object recognition, requires connecting together many neurons in a network and attending to details about handling errors and adjusting weights accordingly.