Article Roundup: Questions on multicore Linux, DO-178B and RTOS performance, How to update legacy automotive designs for functional safety, 5G SoCs Demand New Verification Approaches , Reuse existing verification assets with the Portable Test and Stimulus Standard, Innovations in physical verification and cloud computing keep the IC industry moving forward

- Questions on multicore Linux, DO-178B and RTOS performance

- How to update legacy automotive designs for functional safety

- 5G SoCs Demand New Verification Approaches

- Reuse existing verification assets with the Portable Test and Stimulus Standard

- Siemens and Valor: Two Complementary DFM Technologies

Questions on multicore Linux, DO-178B and RTOS performance

EdaCafe.com

This article talks about the questions on Multicore Linux, DO-178B, RTOS performance and more. An RTOS allows product designers to focus on the added value of their solution while delegating efficient resource (memory, peripheral, etc.) management. In addition to footprint advantages, an RTOS operates with a degree of determinism that is an essential requirement for a variety of embedded applications. Colin Walls explains and compares performances of various RTOSs.

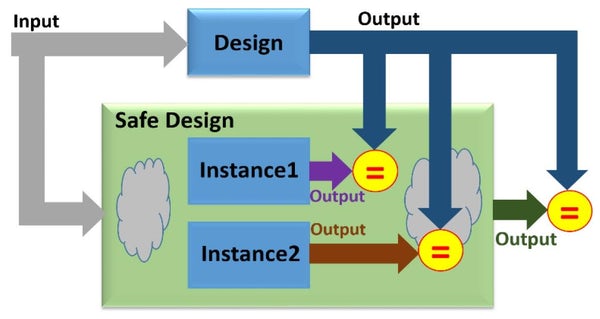

How to update legacy automotive designs for functional safety

TechDesignForums

FMEDA (Failure Mode Effect and Diagnostic Analysis) evaluates the safety architecture with its collection of safety mechanisms and calculates the safety performance of the system. This article talks about how to update legacy automotive designs for functional safety and more.

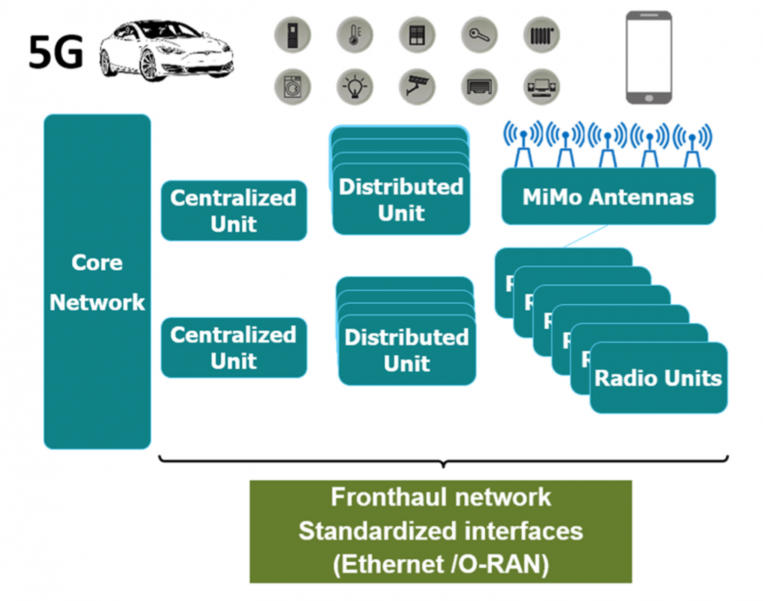

5G SoCs Demand New Verification Approaches

SemiWiki

5G SoCs demand a new verification approach that meets the challenges of the exponential rise in required tests: a verification flow for pre- and post-silicon. The same testbenches and their tests and transactions need to run before and after the silicon is available. In this article, the author explains about the importance of new verification methods and more.

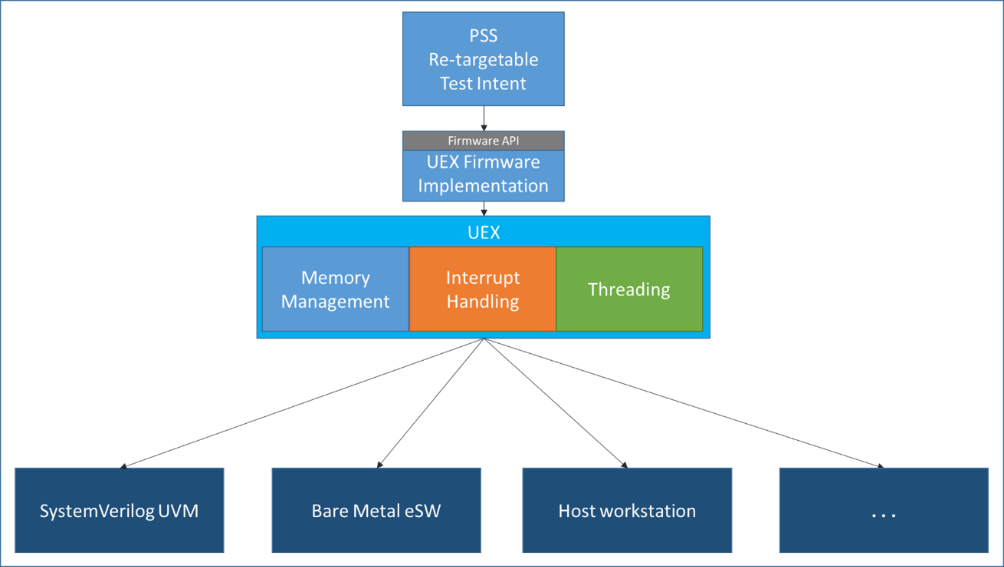

Reuse existing verification assets with the Portable Test and Stimulus Standard

EDN.com

In this article, Mentor’s Matthew Balance explains how to reuse existing verification assets with the Portable Test and Stimulus Standard and more. PSS descriptions capture test intent in a declarative manner. Declarative descriptions, as we’ve seen from the use of the declarative constraint description in System Verilog, lend themselves very nicely to reuse and automation.

In this article, Mentor’s Matthew Balance explains how to reuse existing verification assets with the Portable Test and Stimulus Standard and more. PSS descriptions capture test intent in a declarative manner. Declarative descriptions, as we’ve seen from the use of the declarative constraint description in System Verilog, lend themselves very nicely to reuse and automation.

The format of System Verilog constraints is sufficiently similar to PSS constraints that their reuse can be as simple as copying and pasting the System Verilog constraints into the PSS model.

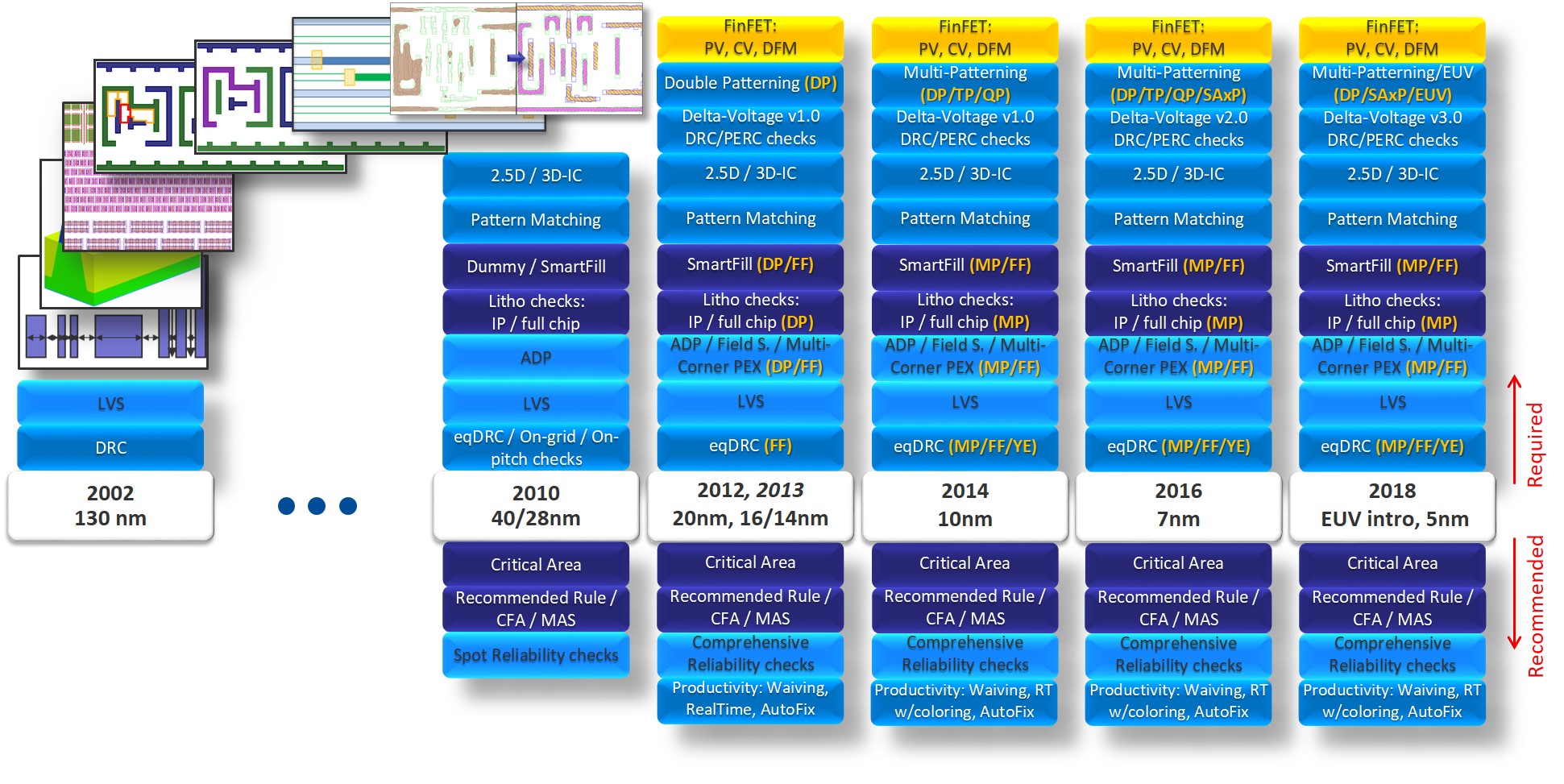

Innovations in physical verification and cloud computing keep the IC industry moving forward

MentorBlogs

Every design company constantly evaluates their design flow and verification tool suite to identify opportunities for faster design development and verification. Time-to-market is a critical commodity in the electronics industry, as is the cost-effective use of resources and engineer expertise.

Replacing inefficient, less precise verification processes with smarter, more accurate, faster, and more efficient functionality can improve both the bottom line and product quality. In this blog, Mentor’s John Ferguson throws light on new approaches to physical verification and more.