Variation Aware Mixed-Signal Verification – your chip’s Yield Shield

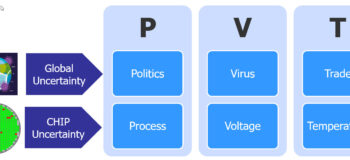

In this time of financial uncertainty, a yield-shield portfolio can protect your investments from market volatility. Uncertainty can be defined as a quantitative measurement of variability in the data [1]. The more the variability in the data – whether its political stability (#election), health (#coronavirus), trade policies, oil prices, employment numbers, the more the uncertainty reflected in the global economy.

The same is true in semiconductor chip manufacturing. Next-generation applications such as AI, automotive, and high-performance computing demand the use of smaller nanometer SoCs to deliver more functionality and higher performance at much lower power. Though smaller geometries bring denser, faster, and cheaper chips there are lots of challenges in manufacturing them. One of the biggest challenges is to measure the impact of process variation on the chip yield. Random process variations tend to affect the electrical characteristics of all transistors in a die/wafer/lot. In addition, there are operating context variations, like voltage & temperature which determine the uncertainty in the operating environment of a particular device during its life span.

Verifying a design across PVT variations is an essential step in design verification. However, there are two tough choices: More simulations or less? To save time and resource we could check designs on a limited number of corners. But, this may not be sufficient and could result in re-spins. Contrarily, simulating and checking AMS designs exhaustively in a continuous PVT space is neither scalable nor practical since the cost of simulations for complex AMS designs can be too expensive and time-consuming.

Mixed-signal simulations tools are primarily written for the functional verification of design to understand the hand-shaking between the digital and the analog components under various test scenarios. To run a variation aware mixed-signal simulation you need a methodology where variability analysis and mixed-signal simulator work in conjunction.

We are pleased to present such a methodology in our On-demand webinar, where our customer, Analog Value Ltd uses Mentor’s tightly integrated Solido Variation Designer and Symphony Mixed-Signal Verification Platform solutions to enable fast variation-aware mixed-signal design and verification of their 2-step time-domain ADC.

Watch On-demand Webinar

[1] NCBI