Article Roundup: UPF Commands, IC Waiver Management, Hybrid Emulation, Reset Domain Crossing & Multi-Patterning at Sub-5nm

- Empowering UPF Commands With Effective Elements Lists

- Automated Waiver Management: Past, Present, and Future

- Hybrid Emulation Takes Center Stage

- A repeatable methodology for modern reset domain crossing issues

- Multi-patterning strategies for navigating the sub-5 nm frontier, part 2

Empowering UPF Commands With Effective Elements Lists

SemiEngineering

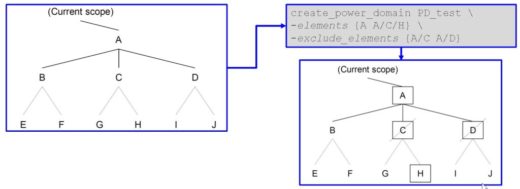

While the unified power format (UPF) is well defined through IEEE 1801 LRM, its more basic features and individual command options can be difficult. This article provides an approach to identifying links between UPF commands through transitive properties of these commands.

While the unified power format (UPF) is well defined through IEEE 1801 LRM, its more basic features and individual command options can be difficult. This article provides an approach to identifying links between UPF commands through transitive properties of these commands.

Automated Waiver Management: Past, Present, and Future

Electronic Design

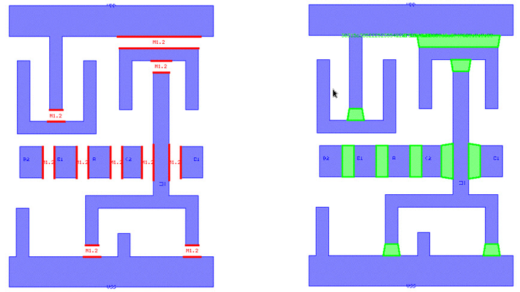

Integrated circuit (IC) layout engineers know that design-rule-checking (DRC) error results are not all equivalent. Some errors are critical and can affect the manufacturing or lifetime reliability of a design, while others are negligible. Design rule waivers are used to ignore certain DRC results where applicable, but manually applying these waivers has become onerous, especially with increasing IP usage. Automated waiver management capabilities help reducing the effort required to capture waiver details for each design.

Integrated circuit (IC) layout engineers know that design-rule-checking (DRC) error results are not all equivalent. Some errors are critical and can affect the manufacturing or lifetime reliability of a design, while others are negligible. Design rule waivers are used to ignore certain DRC results where applicable, but manually applying these waivers has become onerous, especially with increasing IP usage. Automated waiver management capabilities help reducing the effort required to capture waiver details for each design.

Hybrid Emulation Takes Center Stage

SemiEngineering

Chip design complexity continues to increase at a rapid pace, spurred on by AI and other advanced applications. Designs often contain multiple billions of gates, outstretching the capabilities of most verification strategies, at least on their own. Several companies are adopting hybrid emulation approaches to speed up verification despite the growing complexity of modern designs.

A repeatable methodology for modern reset domain crossing issues

Tech Design Forum

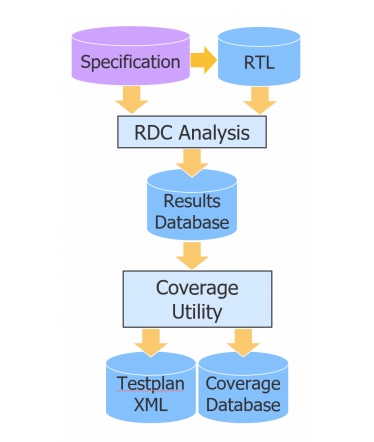

Reset domain crossing (RDC) issues are becoming more common as SoC designs get bigger and more complicated. RDC problems can prevent designs from returning to safe states, causing unreliable start-up or even power overconsumption that can cause irreparable damage. This article examines a repeatable methodology for RDC.

Reset domain crossing (RDC) issues are becoming more common as SoC designs get bigger and more complicated. RDC problems can prevent designs from returning to safe states, causing unreliable start-up or even power overconsumption that can cause irreparable damage. This article examines a repeatable methodology for RDC.

Multi-patterning strategies for navigating the sub-5 nm frontier, part 2

EDN Network

With step-by-step explanations, this series explains the intricacies of self-aligned pattern creation. Understanding these details is key to ensuring layout fidelity in today’s most advanced nodes. Part 1 covered SADP and SAQP. In this concluding installment, the basics of self-aligned litho-etch litho-etch (SALELE) are introduced.