Article Roundup: Orlando’s Digital Twins, Verification & Validation of Vehicle E/E Systems, HLS + IP Accelerates Development, the Nuts and Bolts of Verification & Improving Chip Design

- How Orlando’s Work With Digital Twins May Change How We Engineer Everything

- Achieving Effective Verification and Validation of Vehicle E/E Systems – Part 3

- Catapult HLS integrates eFPGA IP for faster development

- The nuts and bolts of verification: Recasting SystemVerilog for Portable Stimulus

- Utilizing More Data To Improve Chip Design

How Orlando’s Work With Digital Twins May Change How We Engineer Everything

Forbes

Central Florida is a hotbed of digital twin development and research. One of these efforts is a public-private partnership, known as BRIDG, which is focused on bringing microelectronics research to market through silicon wafer fabrication. By partnering with Siemens, BRIDG is one of the first in the semiconductor industry to employ complete digital twins of their components and manufacturing processes.

Central Florida is a hotbed of digital twin development and research. One of these efforts is a public-private partnership, known as BRIDG, which is focused on bringing microelectronics research to market through silicon wafer fabrication. By partnering with Siemens, BRIDG is one of the first in the semiconductor industry to employ complete digital twins of their components and manufacturing processes.

Achieving Effective Verification and Validation of Vehicle E/E Systems – Part 3

Embedded Computing Design

The third installment of this article series looks at testing the digital twin of a vehicle electrical and electronic (E/E) system. The digital twin of an E/E system contains models of all of the ECUs, networks, mechatronic hardware, and more. Test automation software can interface with each of these data types to test the digital twin completely, and accurately.

Catapult HLS integrates eFPGA IP for faster development

Tech Design Forum

Mentor, a Siemens business, is extending the configurability options available from high-level synthesis (HLS) through a collaboration with Menta SAS, a provider of customizable embedded FPGA (eFPGA) IP. The integration will allow design teams to change eFPGA configurations at any stage of development, improving flexibility. The benefits of this integration will be realized particularly in the design of AI-based chips that often undergo multiple iterations.

Mentor, a Siemens business, is extending the configurability options available from high-level synthesis (HLS) through a collaboration with Menta SAS, a provider of customizable embedded FPGA (eFPGA) IP. The integration will allow design teams to change eFPGA configurations at any stage of development, improving flexibility. The benefits of this integration will be realized particularly in the design of AI-based chips that often undergo multiple iterations.

The nuts and bolts of verification: Recasting SystemVerilog for Portable Stimulus

EE World Online

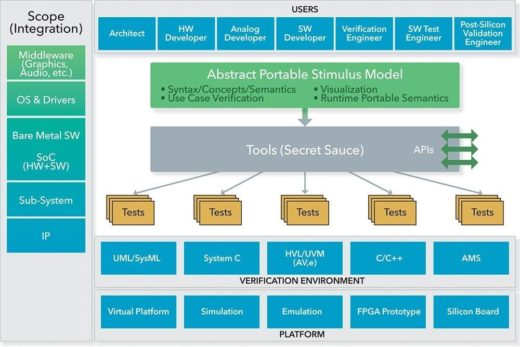

What do nuts, bolts, and the Accellera Portable Stimulus Specification (PSS) have in common? Standardization! Standardization leads to reusability and increased productivity. In part three of this article series, read which SystemVerilog constructs are the easiest to reuse in the PSS.

What do nuts, bolts, and the Accellera Portable Stimulus Specification (PSS) have in common? Standardization! Standardization leads to reusability and increased productivity. In part three of this article series, read which SystemVerilog constructs are the easiest to reuse in the PSS.

Utilizing More Data To Improve Chip Design

SemiEngineering

Designing a new integrated circuit produces a huge amount of data. Some stages of the design process produce more than others, but not all of this data is equally valuable. How should engineers decide what data to capture and loop back in to the flow to improve the reliability of increasingly complex designs?