Article Roundup: Chip Design for New Mobility, Emulation for AI/ML, FPGA Verification Trends, Optimizing Scan-Pattern Ordering & Voltage-Aware DRC

- Chip Design For The Age Of New Mobility

- Hardware Emulation Answers AI/ML Verification Needs

- Trends In FPGA Verification Effort And Adoption: The 2018 Wilson Research Group Functional Verification Study

- Reduce Test/Diagnosis Cost with Optimized Scan-Pattern Ordering

- Use evolving DRC to automate high-voltage and multi-power domain verification

Chip Design For The Age Of New Mobility

SemiEngineering

In the new age of mobility, vehicles are valued more and more for their electronic features instead of mechanical specifications. This is creating a confluence of diverse companies as traditional automotive manufacturers and tech giants like Google prepare to enter the automotive electronics market. For all of these companies, even those familiar with IC design and manufacturing, this space will bring new challenges that require cutting-edge solutions in IC design, verification, test, and more.

In the new age of mobility, vehicles are valued more and more for their electronic features instead of mechanical specifications. This is creating a confluence of diverse companies as traditional automotive manufacturers and tech giants like Google prepare to enter the automotive electronics market. For all of these companies, even those familiar with IC design and manufacturing, this space will bring new challenges that require cutting-edge solutions in IC design, verification, test, and more.

Hardware Emulation Answers AI/ML Verification Needs

EE Web

Chips intended for artificial intelligence and machine learning (AI/ML) applications contain 5-10 billion gates. These large gate counts, along with accelerated time-to-market and hardware-software co-verification, are creating new challenges for chip verification. Hardware emulation provides an answer to these challenges, but not all emulators are created equally. In this article, Dr. Lauro Rizatti examines the important differences between commercially available emulators.

Chips intended for artificial intelligence and machine learning (AI/ML) applications contain 5-10 billion gates. These large gate counts, along with accelerated time-to-market and hardware-software co-verification, are creating new challenges for chip verification. Hardware emulation provides an answer to these challenges, but not all emulators are created equally. In this article, Dr. Lauro Rizatti examines the important differences between commercially available emulators.

Trends In FPGA Verification Effort And Adoption: The 2018 Wilson Research Group Functional Verification Study

SemiEngineering

Harry Foster presents the results of the 2018 Wilson Research Group Functional Verification Study, with a special focus on the FPGA market. FPGA complexity has grown appreciably in the last few years to rival many modern ICs and ASICs. To cope, FPGA projects are forced to mature their verification processes in step.

Reduce Test/Diagnosis Cost with Optimized Scan-Pattern Ordering

Electronic Design

Adjustments to the order in which test patterns are generated and applied can help control the cost of production test. This article presents a methodology for determining the optimal order for test pattern creation to minimize test cost.

Adjustments to the order in which test patterns are generated and applied can help control the cost of production test. This article presents a methodology for determining the optimal order for test pattern creation to minimize test cost.

Use evolving DRC to automate high-voltage and multi-power domain verification

Tech Design Forum

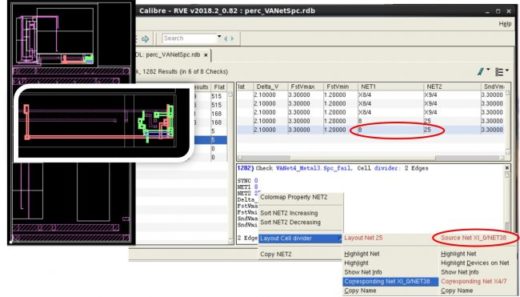

Companies designing chips for high-voltage and multiple power domain applications must achieve the highest levels of accuracy to meet the reliability needs of their market. Automated voltage-aware DRC (VA-DRC) can provide precise and actionable context-aware results to improve design accuracy and help teams meet tight schedules. Read how VA-DRC evolved from previous methods, and how it helps address reliability verification challenges in high-voltage and multiple power domain applications.

Companies designing chips for high-voltage and multiple power domain applications must achieve the highest levels of accuracy to meet the reliability needs of their market. Automated voltage-aware DRC (VA-DRC) can provide precise and actionable context-aware results to improve design accuracy and help teams meet tight schedules. Read how VA-DRC evolved from previous methods, and how it helps address reliability verification challenges in high-voltage and multiple power domain applications.