Article Roundup: Automotive Electronics Safety, DVCon Rundown, DRC Error Reporting, Qualcomm’s DRC Upgrade & Emulation for AI Verification

- How safe is your car?

- AI, Deep Learning, SystemC, UVM, PSS – DVCon Has it All

- A better way to manage error reporting at the chip and block levels

- Qualcomm Attests Benefits of Mentor’s RealTime DRC for P&R

- Verifying AI Designs Thoroughly And Quickly

How safe is your car?

Embedded Computing Design

Modern vehicles are full of electrical and electronic systems that enable a variety of functions ranging from convenience to safety-critical applications. These systems rely on sensors to gather information that determines their operation. While convenience systems, such as climate control, may need only one sensor, safety-critical systems require at least three. Colin Walls explains why in this article.

AI, Deep Learning, SystemC, UVM, PSS – DVCon Has it All

SemiWiki

DVCon is the must-attend industry conference for design and verification engineers, EDA developers, and design managers. This year, sessions will cover topics ranging from artificial intelligence and deep learning, to key features in the new IEEE 1800.2 Standard for UVM. In this article, Daniel Payne covers the highlights of the four day conference.

DVCon is the must-attend industry conference for design and verification engineers, EDA developers, and design managers. This year, sessions will cover topics ranging from artificial intelligence and deep learning, to key features in the new IEEE 1800.2 Standard for UVM. In this article, Daniel Payne covers the highlights of the four day conference.

A better way to manage error reporting at the chip and block levels

Tech Design Forum

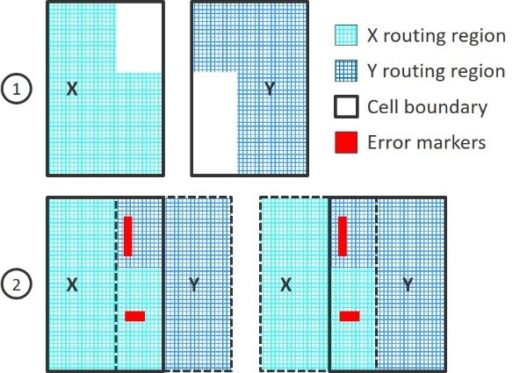

Today, continuous-build environments are the norm for chip designers. In continuous-build environments block and chip-level designers work in parallel, with chip-level designers instantiating incomplete block designs into the chip floorplan. Sometimes this incomplete block data does not comply with DRC, and block-level errors are moved to the chip-level. This article presents techniques to simplify chip-level debug and improve block-level placement by managing error-reporting at the right level.

Today, continuous-build environments are the norm for chip designers. In continuous-build environments block and chip-level designers work in parallel, with chip-level designers instantiating incomplete block designs into the chip floorplan. Sometimes this incomplete block data does not comply with DRC, and block-level errors are moved to the chip-level. This article presents techniques to simplify chip-level debug and improve block-level placement by managing error-reporting at the right level.

Qualcomm Attests Benefits of Mentor’s RealTime DRC for P&R

SemiWiki

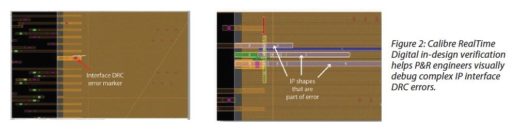

Increasing design sizes have reduced the accuracy of place and route (P&R) tools working from library exchange format cell views, increasing the time needed for whole-chip DRC. Facing this problem, Qualcomm adopted the Calibre RealTime solution to enable incremental DRC in the P&R tool, including all of the layout layers and nested cells and blocks not normally available. With nearly instantaneous feedback on violations and fixes, Qualcomm accelerated signoff DRC to meet tight schedules.

Increasing design sizes have reduced the accuracy of place and route (P&R) tools working from library exchange format cell views, increasing the time needed for whole-chip DRC. Facing this problem, Qualcomm adopted the Calibre RealTime solution to enable incremental DRC in the P&R tool, including all of the layout layers and nested cells and blocks not normally available. With nearly instantaneous feedback on violations and fixes, Qualcomm accelerated signoff DRC to meet tight schedules.

Verifying AI Designs Thoroughly And Quickly

SemiEngineering

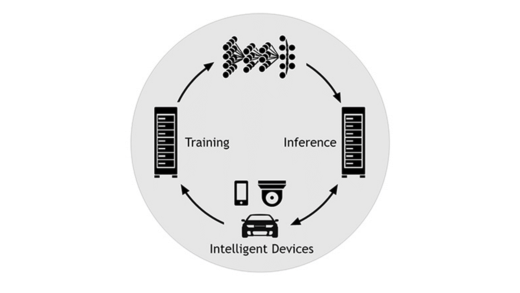

Artificial intelligence (AI) is a hot topic of discussion and innovation as it is moving into a swath of new markets. To verify these complex designs, three key requirements must be met: determinism, scalability, and virtualization. Hardware emulation provides all three, making it a critical technology for AI chip design.

Artificial intelligence (AI) is a hot topic of discussion and innovation as it is moving into a swath of new markets. To verify these complex designs, three key requirements must be met: determinism, scalability, and virtualization. Hardware emulation provides all three, making it a critical technology for AI chip design.