Article Roundup: Generative Design for Automotive Electrical Systems, Emulation for AI, Data Prep & Testing for Big PCBs & Taming Concurrency

- Applying Generative Design to Automotive Electrical Systems

- Emulation for AI: Part One

- Emulation for AI: Part Two

- Mentor and Seica Partner for Data Prep and Testing Big Boards

- Taming Concurrency

Applying Generative Design to Automotive Electrical Systems

SemiWiki

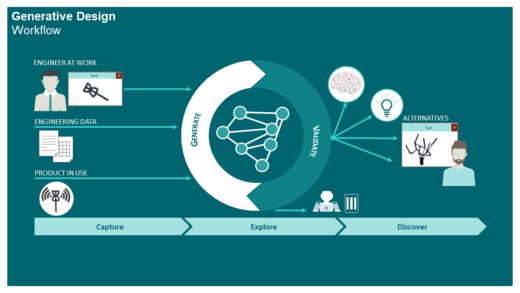

Generative design enables automotive engineers to quickly generate and iterate automotive electrical and electronic system designs. The electrical content of today’s vehicles is increasing as ADAS, autonomous drive, and connectivity continue to develop. Generative design will be a key solution to managing this increased complexity while optimizing a vehicle architecture for weight, power, and performance.

Generative design enables automotive engineers to quickly generate and iterate automotive electrical and electronic system designs. The electrical content of today’s vehicles is increasing as ADAS, autonomous drive, and connectivity continue to develop. Generative design will be a key solution to managing this increased complexity while optimizing a vehicle architecture for weight, power, and performance.

Emulation for AI: Part One

Tech Design Forum

Companies developing artificial intelligence (AI) algorithms are turning to custom ASIC designs based on their algorithms to meet the demanding power and performance requirements of AI. This trend, however, comes with interesting challenges in verification, validation, and system refinement. Emulation will play a key role in addressing these challenges due to its scalability, virtual model support, and determinism.

Emulation for AI: Part Two

Tech Design Forum

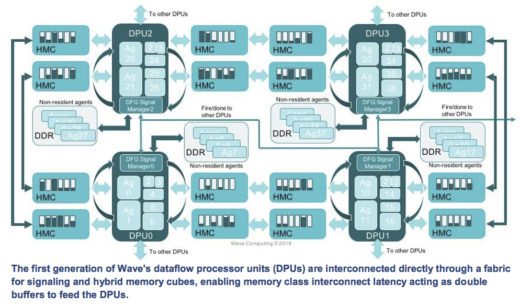

Wave Computing developed their dataflow processing unit (DPU) to provide an AI processing unit that is scalable across multiple nodes and resistant to the fragmentation of AI applications. To verify their designs, Wave had to move from an FPGA-based strategy to emulation. Emulation provided the scalability needed for the multi-billion gate design, and enabled the company to run performance software to test key AI benchmarks.

Wave Computing developed their dataflow processing unit (DPU) to provide an AI processing unit that is scalable across multiple nodes and resistant to the fragmentation of AI applications. To verify their designs, Wave had to move from an FPGA-based strategy to emulation. Emulation provided the scalability needed for the multi-billion gate design, and enabled the company to run performance software to test key AI benchmarks.

Mentor and Seica Partner for Data Prep and Testing Big Boards

IConnect 007

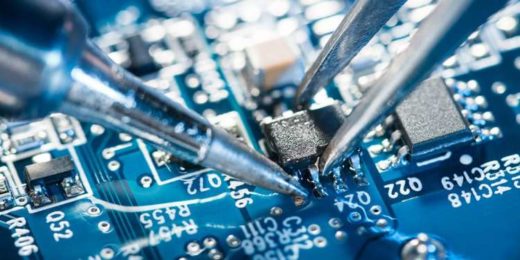

Seica and Mentor have partnered to improve the efficiency of data preparation for testing large printed circuit boards (PCB), accelerating new product introduction (NPI) cycles. This article presents an interview in which Luca Corli, director of sales at Seica, and Mark Laing, business development manager of the Valor division at Mentor, a Siemens Business, discuss this partnership.

Seica and Mentor have partnered to improve the efficiency of data preparation for testing large printed circuit boards (PCB), accelerating new product introduction (NPI) cycles. This article presents an interview in which Luca Corli, director of sales at Seica, and Mark Laing, business development manager of the Valor division at Mentor, a Siemens Business, discuss this partnership.

Taming Concurrency

SemiEngineering

Current EDA solutions struggle to detect deep-seeded bugs that result from concurrency. The severity of this problem will only grow as concurrency and parallelism are relied upon to make-up for the slowing of Moore’s Law. Advancements in high-level synthesis and the Portable Stimulus standard are helping to root out concurrency-related bugs, but significant improvement will only come from unifying hardware and software development, and greater adoption of parallel programming models.