Article Roundup: Mentor on life with Siemens, What Makes a Chip Successful, Computer Vision, SoC Library Characterization & Debug Tops Verification Tasks

- Mentor Graphics on life with Siemens (pt1) & Mentor Graphics on life with Siemens (pt2)

- What Makes A Chip Design Successful Today?

- The Rapid Rise of Computer Vision

- Improving Library Characterization with Machine Learning!

- Debug Tops Verification Tasks

Mentor Graphics on life with Siemens (pt1) & (pt2)

Enterprise IoT Insights

After being acquired, most companies experience a slowdown. This has not been the case for Mentor after its acquisition by Siemens. “We have broken records for all-time growth. And we can attribute that to the financial resources and credibility of Siemens”, said Mentor’s CEO Emeritus, Wally Rhines, at Electronica 2018. This two-part article examines the experience of Mentor as a Siemens business.

After being acquired, most companies experience a slowdown. This has not been the case for Mentor after its acquisition by Siemens. “We have broken records for all-time growth. And we can attribute that to the financial resources and credibility of Siemens”, said Mentor’s CEO Emeritus, Wally Rhines, at Electronica 2018. This two-part article examines the experience of Mentor as a Siemens business.

What Makes A Chip Design Successful Today?

SemiEngineering

In the 90s and early 2000s, transistors were seemingly unlimited. Chips were highly flexible as they contained an excess of transistors, many of which were not used most of the time. Today, companies must differentiate by achieving better design, higher performance, and lower power, which places greater demands on each transistor and makes unused ones very expensive. As a result, the criteria for a successful chip are changing, with an increased focus on field upgradability.

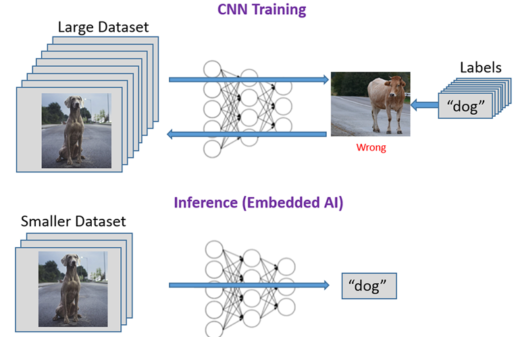

The Rapid Rise of Computer Vision

Electronic Design

Computer vision projects evolve quickly as companies race to reach a completely accurate and reliable hardware-software solution. To keep pace, teams must design and verify algorithms in hardware, under evolving specifications and requirements, without restarting at every change. HLS supports rapid change integration by using constraints and directives to generate RTL from a high level C++ description, leaving the C++ unchanged.

Computer vision projects evolve quickly as companies race to reach a completely accurate and reliable hardware-software solution. To keep pace, teams must design and verify algorithms in hardware, under evolving specifications and requirements, without restarting at every change. HLS supports rapid change integration by using constraints and directives to generate RTL from a high level C++ description, leaving the C++ unchanged.

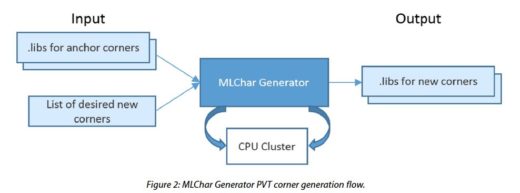

Improving Library Characterization with Machine Learning!

SemiWiki

Creating usable libraries for modern SoC designs has become arduous. Anywhere from ten to one-hundred million simulations are needed to create these libraries that are key to supporting the timing flow of a SoC design. This article looks at a new solution that employs machine learning to accelerate the development of accurate libraries.

Creating usable libraries for modern SoC designs has become arduous. Anywhere from ten to one-hundred million simulations are needed to create these libraries that are key to supporting the timing flow of a SoC design. This article looks at a new solution that employs machine learning to accelerate the development of accurate libraries.

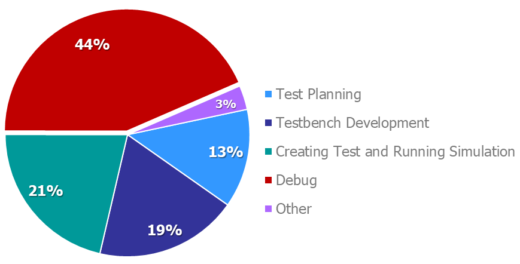

Debug Tops Verification Tasks

SemiEngineering

Forty-four percent of verification engineers’ time is spent in debug, according to a recent survey by the Wilson Research Group. The increasing complexity of chip designs, packaging, and system architectures accounts for some of the increased emphasis on debug, but the process also suffers from some inefficiencies. This article examines new debug technologies aimed at making debug more effective for complex modern designs.

Forty-four percent of verification engineers’ time is spent in debug, according to a recent survey by the Wilson Research Group. The increasing complexity of chip designs, packaging, and system architectures accounts for some of the increased emphasis on debug, but the process also suffers from some inefficiencies. This article examines new debug technologies aimed at making debug more effective for complex modern designs.