Article Roundup: PCB Verification in Schematic & Layout, IIoT Architectural Issues, Gender Stereotypes in Tech, Catching HLS Errors Before RTL & the Demise of Reset Buttons

- Validate Twice, Build Once

- Architectural Issues for Embedded Devices in the IIoT

- Overcoming Gender Stereotypes In Tech

- Catapult Design Checker Finds Coding Errors Before High Level Synthesis

- The demise of the reset button

Validate Twice, Build Once

EE Journal

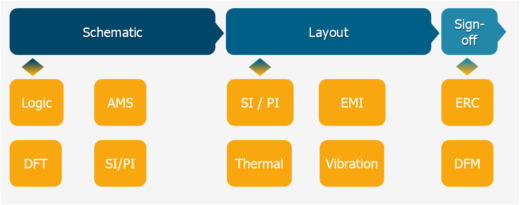

Electronic system design no longer occurs in isolated silos, as new challenges have arisen that require multi-level co-design from board to package to IC. As a result, PCB design tools are expanding to cover multi-board planning, design, and verification. One important new capability is the shifting of verification and validation into the schematic and layout stages to catch errors before they make it into physical prototypes.

Electronic system design no longer occurs in isolated silos, as new challenges have arisen that require multi-level co-design from board to package to IC. As a result, PCB design tools are expanding to cover multi-board planning, design, and verification. One important new capability is the shifting of verification and validation into the schematic and layout stages to catch errors before they make it into physical prototypes.

Architectural Issues for Embedded Devices in the IIoT

Electronic Design

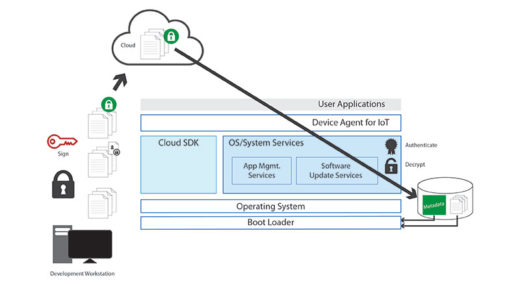

Gaps between the functionality provided by cloud provider software development kits (SDKs) and the functionality needed at the device level are impeding the adoption of IIoT capabilities. These gaps center on device management, health monitoring, diagnostics, security, and more. This article examines a commercial IIoT solution that bridges these gaps to enable broader and more streamlined IIoT implementation.

Gaps between the functionality provided by cloud provider software development kits (SDKs) and the functionality needed at the device level are impeding the adoption of IIoT capabilities. These gaps center on device management, health monitoring, diagnostics, security, and more. This article examines a commercial IIoT solution that bridges these gaps to enable broader and more streamlined IIoT implementation.

Overcoming Gender Stereotypes In Tech

SemiEngineering

Gender inequality issues in the high tech field are highly complex and often ingrained in ways that make them difficult to perceive. This article examines these issues through the perspectives of six women in senior positions at six different high tech companies, including Mentor’s Karen Donlan. While many programs and initiatives have been established to address these challenges, some issues persist.

Catapult Design Checker Finds Coding Errors Before High Level Synthesis

SemiWiki

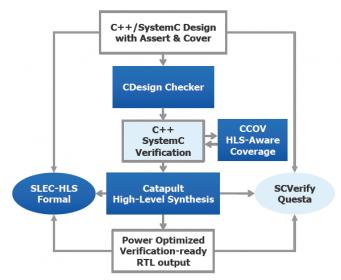

In high-level synthesis (HLS), inaccuracies or ambiguities in the C++ code lead to mismatches between the high-level description and RTL during simulation. Design teams need a tool that can quickly check for bugs and suboptimal code before synthesizing to RTL. Catapult Design Checker accomplishes this using static and formal verification to uncover problems, such as uninitialized memory reads, before RTL.

In high-level synthesis (HLS), inaccuracies or ambiguities in the C++ code lead to mismatches between the high-level description and RTL during simulation. Design teams need a tool that can quickly check for bugs and suboptimal code before synthesizing to RTL. Catapult Design Checker accomplishes this using static and formal verification to uncover problems, such as uninitialized memory reads, before RTL.

The demise of the reset button

Embedded Computing Design

Embedded systems are typically very reliable, but the possibility of failures is always present. Lock-up is a common failure mode in which the device freezes and is unresponsive to user input. The solution to lock-up is often to cut the power to the device, but how do you achieve this with the many battery-powered devices we carry today, which usually no longer feature a reset button.