Article Roundup: Semiconductor Market Drivers, Formal Verification for Data-Path Applications, Frontloading CFD, Interface DRC & Advanced Node Parasitic Extraction

- New Market Drivers – Part 1

- Extend formal property verification to protocol-driven datapaths

- Frontloading CFD Is a Win for Business

- Interface DRC Can Streamline Chip-Level Interface Physical Verification

- Parasitic extraction must solve advanced node issues

New Market Drivers – Part 1

SemiEngineering

The semiconductor market is undergoing a shift in its primary driving force. The IoT and autonomous drive are supplanting mobile technology as the key enabler of semiconductor advancement. Luckily, many of the lessons learned during the mobile era can be applied today and in the future. This article recaps a roundtable discussion with experts from EDA and semiconductor companies on the transition to an automotive and IoT-driven market, and the implications of this shift for semiconductor design.

Extend formal property verification to protocol-driven datapaths

Tech Design Forum

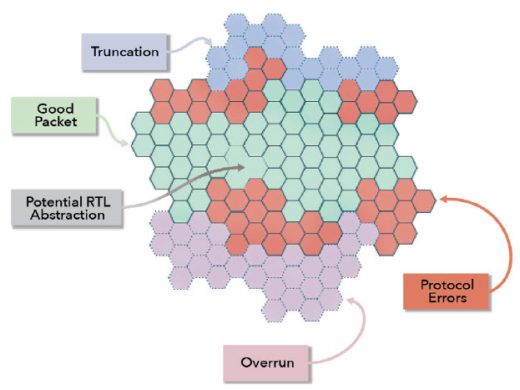

Protocol verification is a challenge for any testbench due to dynamic packet sizes and complex error scenarios. Trying to define the large array of packet sizes and configurations within a formal testbench can make it feel impossible. This article explains how sound, upfront planning and an understanding of likely spots for errors and difficulties unlocks the promise of formal verification for data-path applications.

Protocol verification is a challenge for any testbench due to dynamic packet sizes and complex error scenarios. Trying to define the large array of packet sizes and configurations within a formal testbench can make it feel impossible. This article explains how sound, upfront planning and an understanding of likely spots for errors and difficulties unlocks the promise of formal verification for data-path applications.

Frontloading CFD Is a Win for Business

Digital Engineering

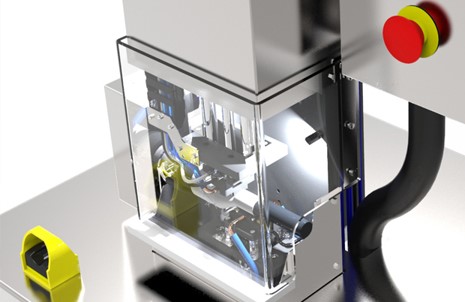

CAD-embedded CFD solutions enable engineers and designers to perform thermal simulations and analyses early in their design process. As a result, it is often lauded as a key to boosting design efficiency, productivity, and accuracy. However, it can even be used as an effective marketing tool. Read how one business owner leverages 3D CFD to inform and excite potential and returning customers, extending the technology’s benefits from engineering to the broader business.

CAD-embedded CFD solutions enable engineers and designers to perform thermal simulations and analyses early in their design process. As a result, it is often lauded as a key to boosting design efficiency, productivity, and accuracy. However, it can even be used as an effective marketing tool. Read how one business owner leverages 3D CFD to inform and excite potential and returning customers, extending the technology’s benefits from engineering to the broader business.

Interface DRC Can Streamline Chip-Level Interface Physical Verification

SemiEngineering

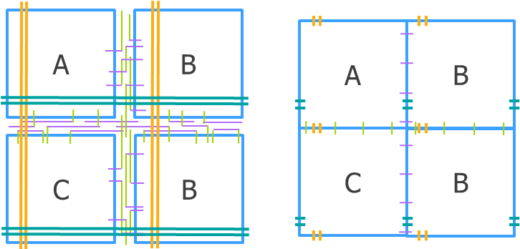

Validating the chip-level interconnect and block interfaces without generating a multitude of invalid DRC results can save time and help teams meet aggressive tapeout schedules. Designers can achieve this by implementing an interim interface DRC that excludes rules and data that are unreliable when checked with incomplete blocks. Adopting an interface DRC checking flow will shorten DRC runtime and debug sessions, and increase confidence in the design verification.

Validating the chip-level interconnect and block interfaces without generating a multitude of invalid DRC results can save time and help teams meet aggressive tapeout schedules. Designers can achieve this by implementing an interim interface DRC that excludes rules and data that are unreliable when checked with incomplete blocks. Adopting an interface DRC checking flow will shorten DRC runtime and debug sessions, and increase confidence in the design verification.

Parasitic extraction must solve advanced node issues

EDN Network

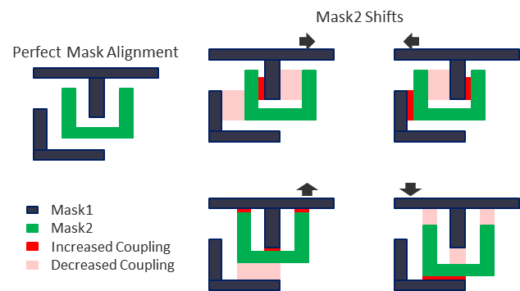

The move to more advanced process nodes increases performance and functionality, but simultaneously increases the parasitic interactions between neighboring geometries. New parasitic extraction processes for interconnect modeling ensure accurate capture of parasitic and layout-dependent effects for non-planar devices, and provide more efficient netlist input to downstream analysis. With these advanced parasitic extraction solutions, designers can fully leverage the benefits of advanced node designs.

The move to more advanced process nodes increases performance and functionality, but simultaneously increases the parasitic interactions between neighboring geometries. New parasitic extraction processes for interconnect modeling ensure accurate capture of parasitic and layout-dependent effects for non-planar devices, and provide more efficient netlist input to downstream analysis. With these advanced parasitic extraction solutions, designers can fully leverage the benefits of advanced node designs.