Article Roundup: Automatic SerDes Validation, Hardware Emulation History, Data Buffering, CFD for EVs & Thermal Monitoring on Advanced ICs

- HyperLynx update automates SerDes validation

- Dipping in the Hardware Emulation Archives

- Data Buffering’s Role Grows

- Design Essentials: Harnessing the Power of Simulation for EV Design

- New Thermal Issues Emerge

HyperLynx update automates SerDes validation

Tech Design Forum

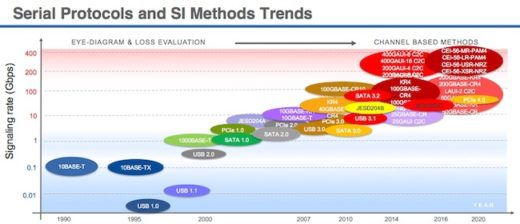

You can now perform high-speed SerDes channel validation without being a signal integrity or electromagnetic simulation expert. HyperLynx can decompose a channel into 2.5D and 3D components for modeling and compliance checking across more than 25 SerDes protocols. Coupled with the HyperLynx 3D Explorer for topology exploration & optimization, these new technologies will accelerate design flows and reduce reliance on the limited supply of signal integrity, electromagnetic, and 3D full-wave solver experts.

You can now perform high-speed SerDes channel validation without being a signal integrity or electromagnetic simulation expert. HyperLynx can decompose a channel into 2.5D and 3D components for modeling and compliance checking across more than 25 SerDes protocols. Coupled with the HyperLynx 3D Explorer for topology exploration & optimization, these new technologies will accelerate design flows and reduce reliance on the limited supply of signal integrity, electromagnetic, and 3D full-wave solver experts.

Dipping in the Hardware Emulation Archives

Electronic Design

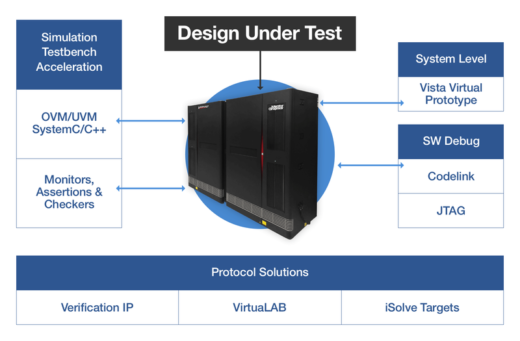

Hardware emulation is now a key step in an increasing number of chip verification flows. This wasn’t always the case. Emulation, originally, took a long time to set up, provided poor visibility into the DUT, and was slow to compile. The development of custom emulation FPGA’s and processors, as well as advances in off-the-shelf varieties, enabled totally DUT visibility, easier set up, and faster compilation, making emulation a necessity for chip design verification.

Hardware emulation is now a key step in an increasing number of chip verification flows. This wasn’t always the case. Emulation, originally, took a long time to set up, provided poor visibility into the DUT, and was slow to compile. The development of custom emulation FPGA’s and processors, as well as advances in off-the-shelf varieties, enabled totally DUT visibility, easier set up, and faster compilation, making emulation a necessity for chip design verification.

Data Buffering’s Role Grows

SemiEngineering

Read industry experts’ views, including Mentor’s Randy Allen, on data buffering technology as a way to speed up the processing of increasingly large quantities of data. Specifically, data buffering provides temporary physical memory to store incoming data, smoothing uneven data rates while also providing additional memory capacity, bandwidth, enhanced RAS, and more. However, designers must consider whether use a discrete data buffering chip, or to integrate it into the SoC as each has implications for power, system latency, and the required expertise of the designer.

Design Essentials: Harnessing the Power of Simulation for EV Design

Machine Design

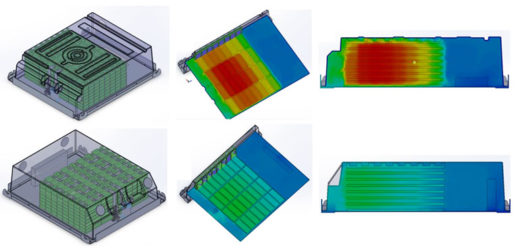

A primary focus of electric vehicle design is optimizing the battery pack and electric powertrain to maximize drive range while supporting the many in-cabin amenities. CFD software for designers enables this optimization to begin at initial design and prototyping, reducing the time and cost of development up to 60%. This article provides examples of a frontloaded CFD design flow for a battery pack, traction motor, and power-electronics thermal simulation.

A primary focus of electric vehicle design is optimizing the battery pack and electric powertrain to maximize drive range while supporting the many in-cabin amenities. CFD software for designers enables this optimization to begin at initial design and prototyping, reducing the time and cost of development up to 60%. This article provides examples of a frontloaded CFD design flow for a battery pack, traction motor, and power-electronics thermal simulation.

New Thermal Issues Emerge

SemiEngineering

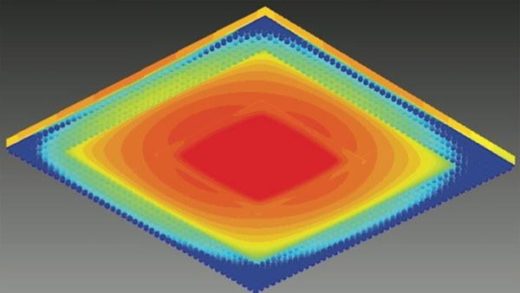

IC gate density on advanced process nodes is increasing the need for thermal monitoring and optimization on chips. Heightened temperatures threaten the reliability of chips, a major concern for automotive ICs that must function consistently in extreme conditions. Additionally, the thermal behavior of these chips must be considered in the context of larger systems to predict thermal hotspots and maximize chip reliability.

IC gate density on advanced process nodes is increasing the need for thermal monitoring and optimization on chips. Heightened temperatures threaten the reliability of chips, a major concern for automotive ICs that must function consistently in extreme conditions. Additionally, the thermal behavior of these chips must be considered in the context of larger systems to predict thermal hotspots and maximize chip reliability.